# Asynchronous Sequential Logic

UNIT-5

### Synchronous Sequential Circuits

The change of internal state occurs in response to the synchronized clock pulse.

Memory elements are clocked flip-flops.

### Asynchronous Sequential Circuits

The change of internal state occurs when there is a change in the input variables.

Memory elements are unclocked flip-flops or timedelay elements.

### Synchronous Sequential Circuits

Timing problems are eliminated by triggering all flip-flops with pulse edge.

### Asynchronous Sequential Circuits

Care must be taken to ensure that each new state is stable even though a feedback path exists.

Higher speed, More economical

### Asynchronous Sequential Circuits

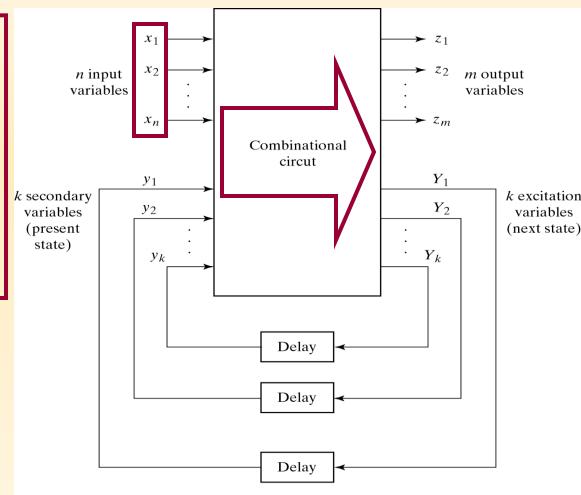

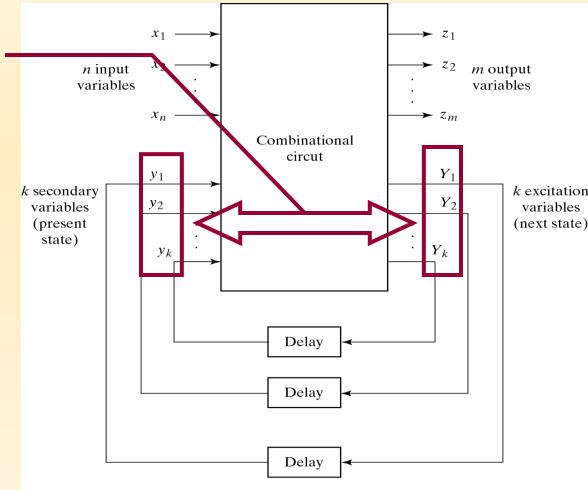

When an input variable changes in value, the y secondary variables do not change instantaneously.

Fig. 9-1 Block Diagram of an Asynchronous Sequential Circuit

### Asynchronous Sequential Circuits

In steady-state condition, the y's and the Y's are the same, but during transition they are not.

Fig. 9-1 Block Diagram of an Asynchronous Sequential Circuit

#### fundamental mode

fundamental mode: Only one input variable can change at any one time and the time between two input changes must be longer than the time it takes the circuit to reach a stable state.

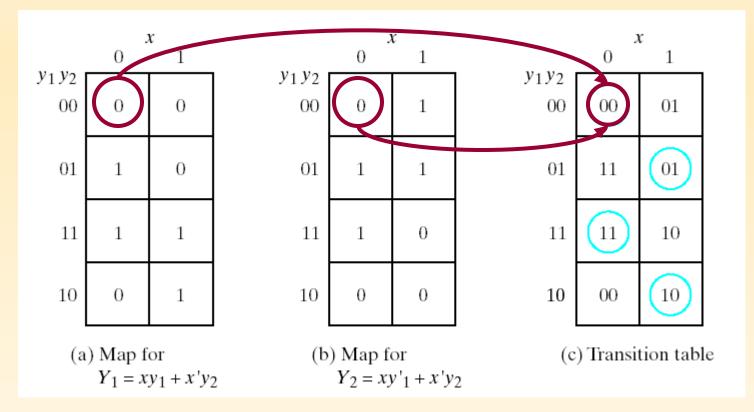

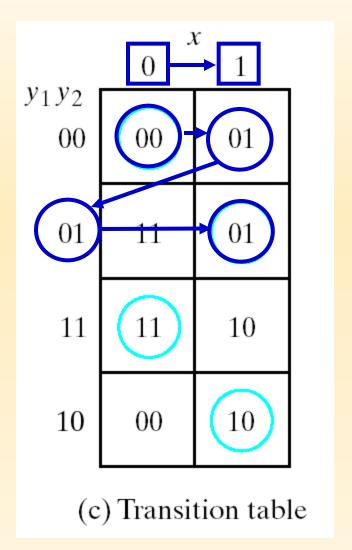

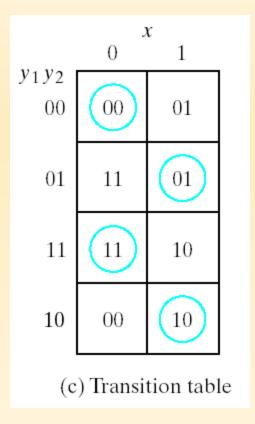

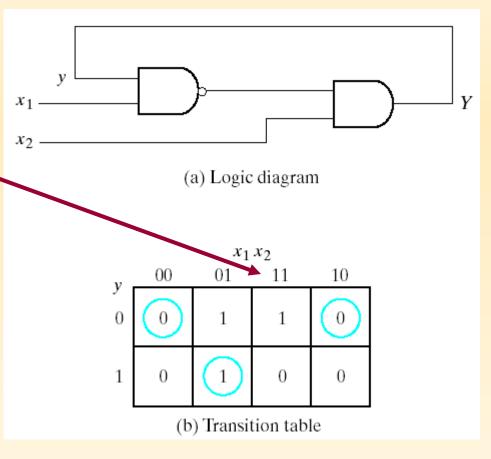

#### **Transition Table**

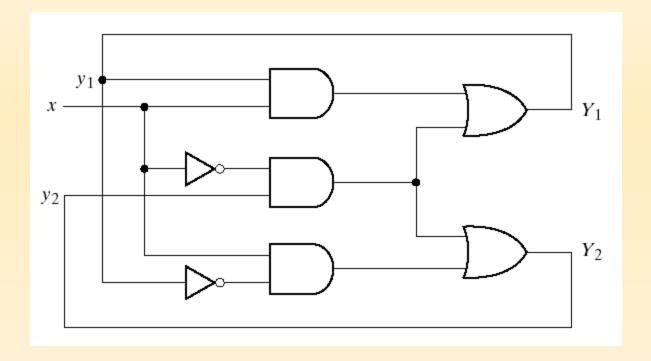

$$Y_1 = xy_1 + x'y_2$$

$$Y_2 = xy'_1 + x'y_2$$

#### **Transition Table**

$$Y_1 = xy_1 + x'y_2$$

$$Y_2 = xy'_1 + x'y_2$$

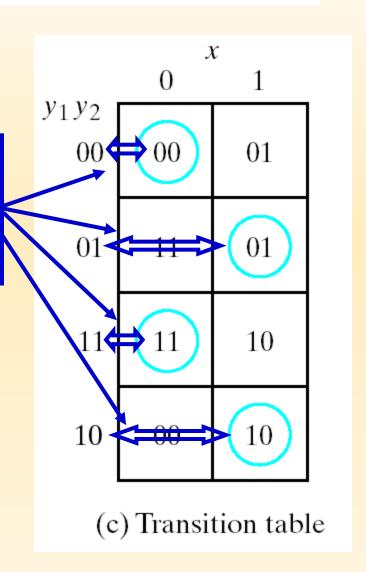

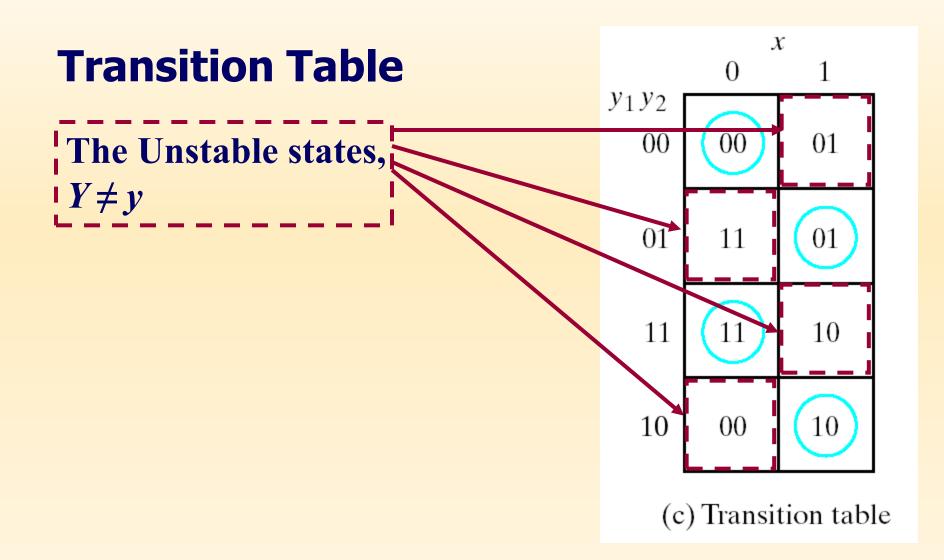

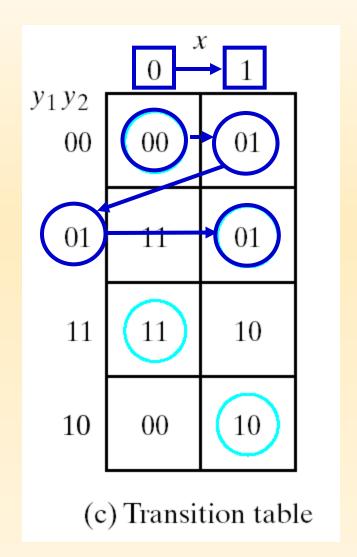

#### **Transition Table**

For a state to be stable, the value of Y must be the same as that of  $y = y_1y_2$

#### **Transition Table**

Consider the square for x = 0 and y = 00. It is stable.

x changes from 0 to 1.

The circuit changes the value of Y to 01. The state is unstable.

The feedback causes a change in y to 01. The circuit reaches stable.

#### **Transition Table**

In general, if a change in the input takes the circuit to an unstable state, y will change until it reaches a stable state.

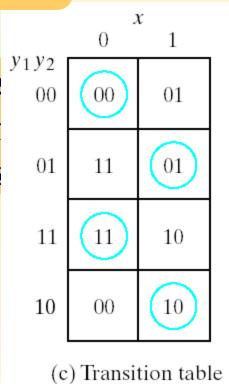

#### Flow Table

Flow Table

table whoseby letter synbinary values

#### **Flow Table**

It is called primitive flow table because it has only one stable state in each row.

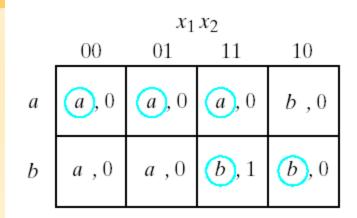

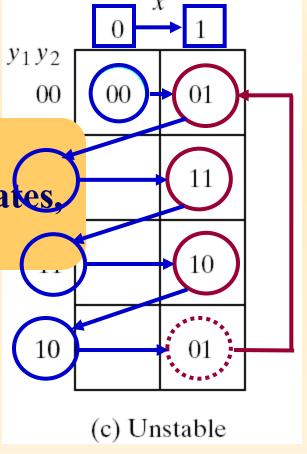

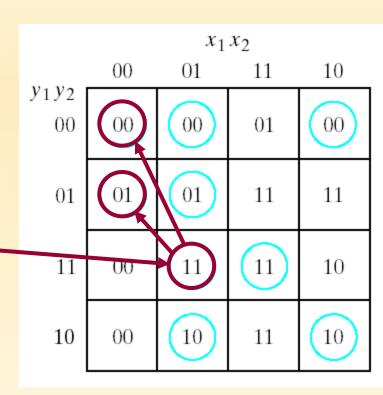

(b) Two states with two inputs and one output

It is a flow table with more than one stable state in the same row.

#### **Flow Table**

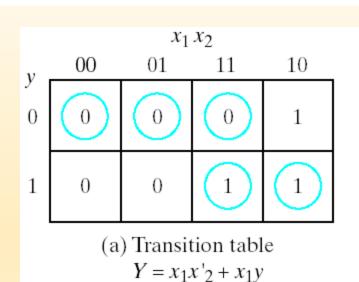

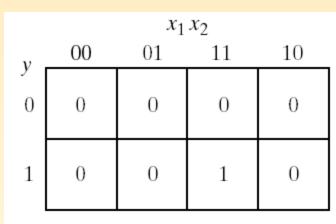

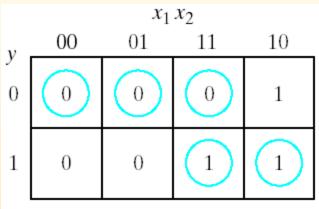

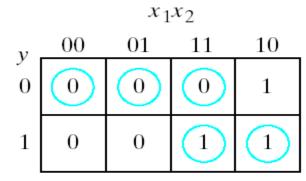

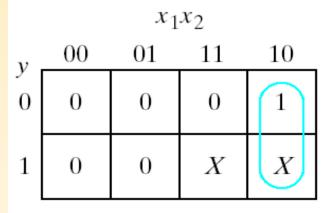

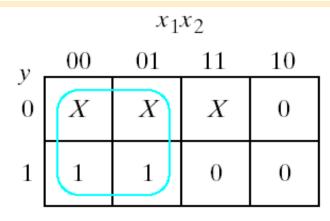

(b) Map for output  $z = x_1 x_2 y$

(a) Transition table  $Y = x_1x_2 + x_1y$

|   | $x_1 x_2$ |    |    |    |  |  |

|---|-----------|----|----|----|--|--|

| y | 00        | 01 | 11 | 10 |  |  |

| 0 | 0         | 0  | 0  | 0  |  |  |

| 1 | 0         | 0  | 1  | 0  |  |  |

(b) Map for output

$$z = x_1 x_2 y$$

#### **Race Conditions**

Noncritical Race:

Two or more binary state variables

State variables change trame a response to a change

to 11. The possible transcould be

00

11

00

01

11

00

10

11

It is a noncritical race. The final stable state that the circuit reaches does not depend on the order in which the state variables change.

#### **Race Conditions**

#### Critical Race:

State variables change from 00 to 11. The possible transition could be

|                | <i>د</i><br>0 | ;<br>1 |  |

|----------------|---------------|--------|--|

| $y_1 y_2 = 00$ | 00            | 11     |  |

| 01             |               | 11     |  |

00

11

00

01

11

00

10

It is a critical race. The final stable state depends on the order in which the state variables change.

(b) Possible transitions:

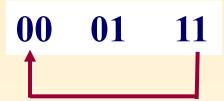

#### **Race Conditions**

Cycle

When a circuit goes through a unique sequence of unstable states, it is said to have a cycle.

The sequence is as follows,

### **Stability Consideration**

Column 11 has no stable state. With input  $x_1 x_2 = 11$ , Y and y are never the same.

This will cause instability.

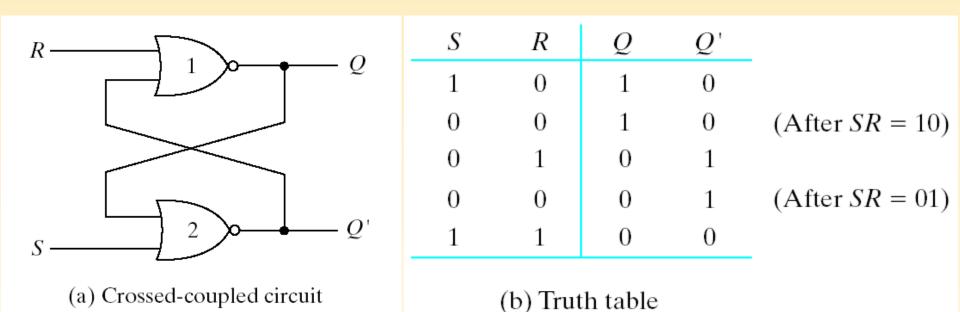

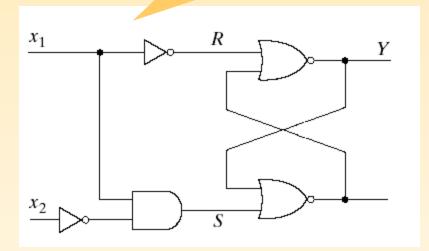

#### **SR** Latch

The circuit diagram and truth table of the *SR* latch are shown as follows,

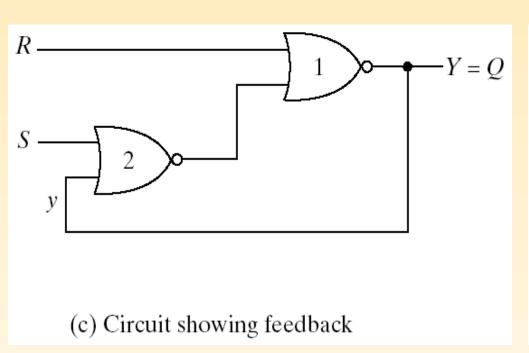

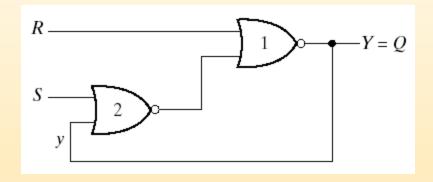

#### **SR** Latch

The circuit diagram of the *SR* latch can be redrawn as follows,

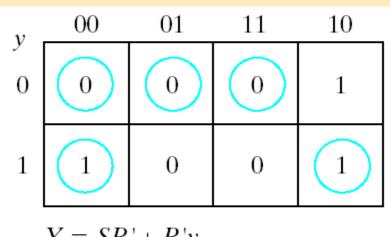

$$Y = SR' + R'y$$

$$Y = S + R'y \text{ when } SR = 0$$

(d) Transition table

#### **SR** Latch

$$Y = [(S + y)' + R]'$$

=  $(S + y)R' = SR' + R'y$

$$SR' + SR = S(R' + R) = S$$

$$SR = 0$$

$$SR' = S$$

$$Y = SR' + R'y = S + R'y \quad \text{when } SR = 0$$

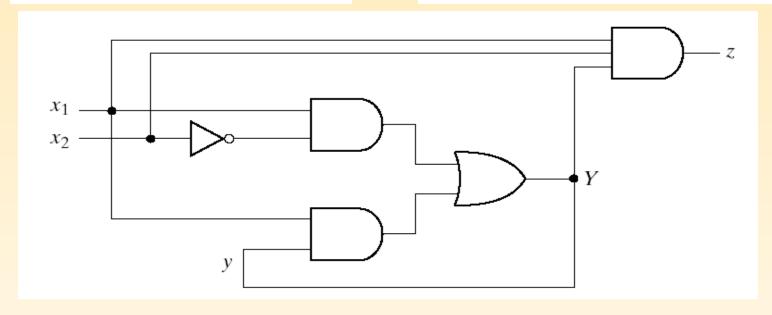

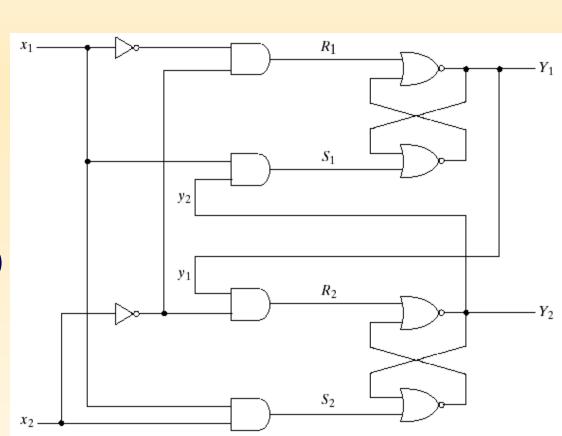

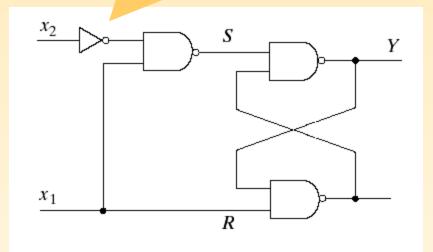

#### **Analysis Example**

$$S_1 = x_1 y_2$$

$$S_2 = x_1 x_2$$

$$R_1 = x'_1 x'_2$$

$$R_2 = x'_2 y_1$$

$$S_1 R_1 = x_1 y_2 x_1' x_2' = 0$$

$$S_2 R_2 = x_1 x_2 x_2 y_1 = 0$$

#### **Analysis Example**

$$Y_1 = S_1 + R'_1 y_1 = x_1 y_2 + (x_1 + x_2) y_1$$

$$Y_2 = S_2 + R'_2 y_2 = x_1 x_2 + (x_2 + y'_1) y_2$$

There is a critical race condition

#### **Latch Excitation Table**

A table that lists the required inputs S and R for each of the possible transitions from y to Y

The first two columns list the four possible transitions from y to Y.

| y | Y | S | R |

|---|---|---|---|

| 0 | 0 | 0 | X |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | X | 1 |

(b) Latch excitation table

The next two columns specify the required input values that will result in the specified transition.

### **Implementation Example**

(a) Transition table  $Y = x_1x'_2 + x_1y$

| y | Y | S | R |

|---|---|---|---|

| 0 | 0 | 0 | X |

| O | 1 | 1 | O |

| 1 | O | 0 | 1 |

| 1 | 1 | X | 1 |

(b) Latch excitation table

(c) Map for  $S = x_1x'_2$

(d) Map for  $R = x'_1$

### **Implementation Example**

$$S = x_1 x_2 \qquad R = x_1'$$

Circuit with NOR latch

Circuit with NAND latch

### **Design Example**

Design a gated latch circuit with t and D (data), and one output Q.

**Gated-Latch Total States**

te)

|                            | Inp | uts | Output |                       |

|----------------------------|-----|-----|--------|-----------------------|

| State                      | D   | G   | Q      | comments              |

| а                          | 0   | 1   | 0      | D = Q because $G = 1$ |

| b                          | 1   | 1   | 1      | D = Q because $G = 1$ |

| $\boldsymbol{\mathcal{C}}$ | 0   | 0   | 0      | After state a or d    |

| d                          | 1   | 0   | 0      | After state <i>c</i>  |

| e                          | 1   | 0   | 1      | After state b or f    |

| f                          | 0   | 0   | 1      | After state e         |

### **Design Example**

|                  | Inputs |   | Output |

|------------------|--------|---|--------|

| State            | D      | G | Q      |

| а                | 0      | 1 | 0      |

| b                | 1      | 1 | 1      |

| $\boldsymbol{c}$ | 0      | 0 | 0      |

| d                | 1      | 0 | 0      |

| e                | 1      | 0 | 1      |

| f                | 0      | 0 | 1      |

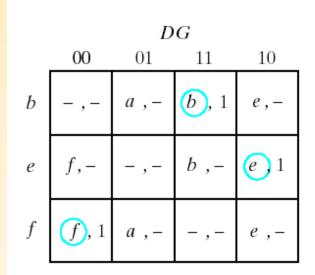

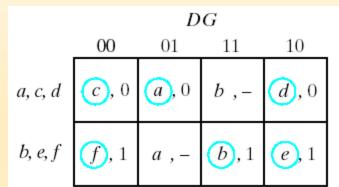

|   | DG             |              |                                |              |  |  |

|---|----------------|--------------|--------------------------------|--------------|--|--|

|   | 00             | 01           | 11                             | 10           |  |  |

| а | c,-            | <b>a</b> , 0 | b ,-                           | - ,-         |  |  |

| b | -,-            | a ,-         | <b>(</b> <i>b</i> <b>)</b> , 1 | e,-          |  |  |

| С | <b>c</b> , 0   | a ,-         | -,-                            | d ,-         |  |  |

| d | c,-            | -,-          | b ,-                           | <b>d</b> , 0 |  |  |

| е | f,-            | - ,-         | b ,-                           | <b>e</b> , 1 |  |  |

| f | <b>(</b> f), 1 | a ,-         | - ,-                           | e ,-         |  |  |

D

Two of more rows in the primitive flow table can be merged into one row if there are non-conflicting states and outputs in each of the columns.

Reduction outputs in each Primitive Flov

|   | DG             |              |                                |              |  |  |

|---|----------------|--------------|--------------------------------|--------------|--|--|

|   | 00             | 01           | 11                             | 10           |  |  |

| а | c , –          | <b>a</b> , 0 | b ,-                           | - ,-         |  |  |

| b | -,-            | a ,-         | <b>(</b> <i>b</i> <b>)</b> , 1 | e,-          |  |  |

| С | <b>c</b> , 0   | a ,-         | - ,-                           | d ,-         |  |  |

| d | c,-            | -,-          | b ,-                           | <b>d</b> , 0 |  |  |

| e | f,-            | - ,-         | b ,-                           | <b>e</b> , 1 |  |  |

| f | <b>(</b> f), 1 | a ,-         | - ,-                           | e ,-         |  |  |

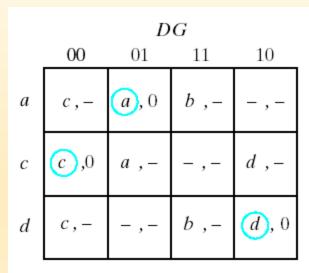

|   | DG          |              |      |                |  |

|---|-------------|--------------|------|----------------|--|

|   | 00          | 01           | 11   | 10             |  |

| а | с,-         | <b>a</b> , 0 | b ,- | - ,-           |  |

| c | <b>c</b> ,0 | a ,-         | -,-  | d ,-           |  |

| d | c,-         | - ,-         | b ,- | <b>(d)</b> , 0 |  |

### **Reduction of the Primitive Flow Table**

|   | DG                             |              |                                |                                |  |

|---|--------------------------------|--------------|--------------------------------|--------------------------------|--|

|   | 00                             | 01           | 11                             | 10                             |  |

| а | <b>(a)</b> , 0                 | <b>a</b> , 0 | b ,-                           | (a), 0                         |  |

| b | <b>(</b> <i>b</i> <b>)</b> , 1 | a ,-         | <b>(</b> <i>b</i> <b>)</b> , 1 | <b>(</b> <i>b</i> <b>)</b> , 1 |  |

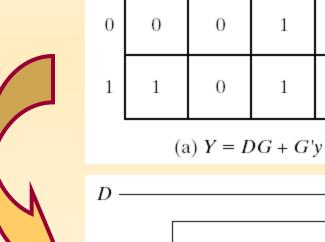

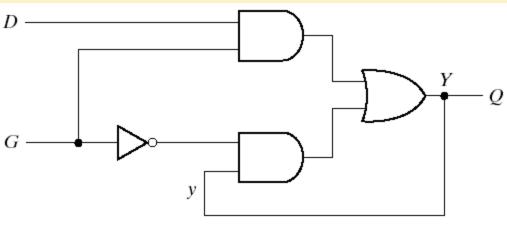

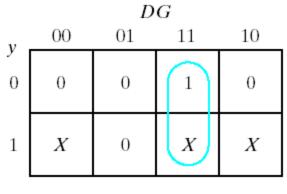

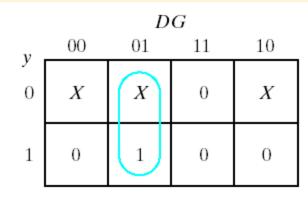

### **Transition Table and Logic Diagram**

DG

|             | DG |    |    |    |  |  |

|-------------|----|----|----|----|--|--|

| y           | 00 | 01 | 11 | 10 |  |  |

| 0           | 0  | 0  | 1  | 0  |  |  |

| 1           | 1  | 0  | 1  | 1  |  |  |

| (b) $Q = Y$ |    |    |    |    |  |  |

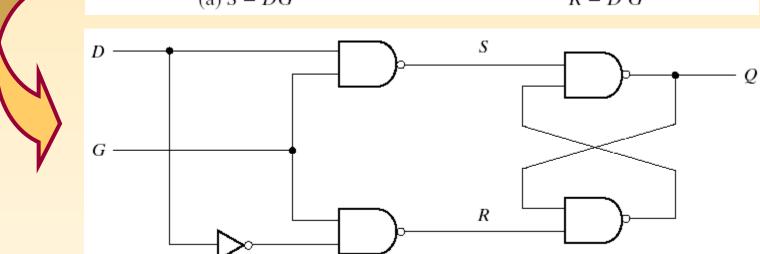

#### Circuit With SR Latch

| (a) | S | = | DG    |

|-----|---|---|-------|

| (4) | 9 |   | $\nu$ |

$$R = D'G$$

### **Assigning Output to Unstable States**

- 1. Assign a 0 to an output variable associated with an unstable state that is a transient state between two stable states that have a 0 in the corresponding output variable.

- 2. Assign a 1 to an output variable associated with an unstable state that is a transient state between two stable states that have a 1 in the corresponding output variable.

- 3. Assign a don't-care condition to an output variable associated with an unstable state that is a transient state between two stable states that have different values in the corresponding output variable.

### **Reduction of State and Flow Tables**

### **Equivalent States**

Two states are equivalent if for each possible input, they give exactly the same output and go to the same next states or to equivalent next states.

The characteristic of equivalent states is that if (a,b) imply (c,d) and (c,d) imply (a,b), then both pairs of states are equivalent.

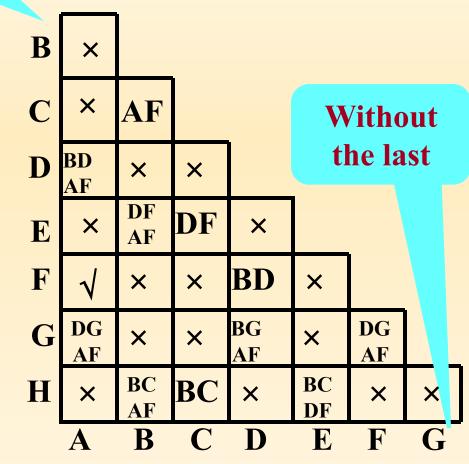

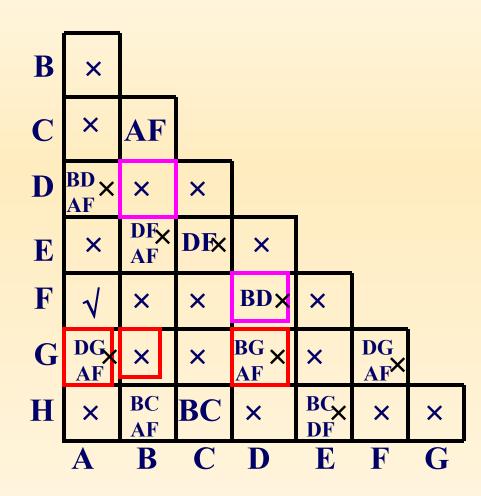

#### **Implication Table**

Two states are equivalent if for each possible input, they give exactly the same output and go to the same next states or to equivalent next states.

The characteristic of equivalent states is that if (a,b) imply (c,d) and (c,d) imply (a,b), then both pairs of states are equivalent.

#### **Implication**

Without the first

| Example |

|---------|

|---------|

| $S_n$ | 00          | 01          | 11          | 10         |

|-------|-------------|-------------|-------------|------------|

| A     | <b>D</b> /0 | <b>D</b> /0 | F/0         | <b>A/0</b> |

| B     | <b>C</b> /1 | <b>D</b> /0 | <b>E/1</b>  | <b>F/0</b> |

| C     | <b>C</b> /1 | <b>D</b> /0 | E/1         | <b>A/0</b> |

| D     | <b>D</b> /0 | <b>B</b> /0 | <b>A/0</b>  | F/0        |

| E     | <b>C</b> /1 | F/0         | E/1         | <b>A/0</b> |

| F     | <b>D</b> /0 | <b>D</b> /0 | <b>A/0</b>  | F/0        |

| G     | <b>G</b> /0 | <b>G</b> /0 | <b>A/0</b>  | <b>A/0</b> |

| H     | <b>B</b> /1 | <b>D</b> /0 | <b>E</b> /1 | <b>A/0</b> |

$$S_{n+1}/Z_n$$

#### **Implied Pairs**

| example       |                                                         |                |             |                |  |  |  |

|---------------|---------------------------------------------------------|----------------|-------------|----------------|--|--|--|

| $S_n$         | $\begin{bmatrix} X_1 X_2 \\ S_n \end{bmatrix}$ 00 01 11 |                |             |                |  |  |  |

| A             | <b>D</b> /0                                             | <b>D</b> /0    | <b>F</b> /0 | <b>A/0</b>     |  |  |  |

| B             | <b>C</b> /1                                             | $\mathbf{D}/0$ | <b>E</b> /1 | <b>F</b> /0    |  |  |  |

| C             | <b>C</b> /1                                             | $\mathbf{D}/0$ | <b>E</b> /1 | $\mathbf{A}/0$ |  |  |  |

| $\mathbf{D}$  | <b>D</b> /0                                             | <b>B</b> /0    | <b>A</b> /0 | <b>F/0</b>     |  |  |  |

| E             | <b>C</b> /1                                             | <b>F/0</b>     | <b>E/1</b>  | A/0            |  |  |  |

| $\mathbf{F}$  | <b>D</b> /0                                             | $\mathbf{D}/0$ | <b>A/0</b>  | <b>F/0</b>     |  |  |  |

| G             | G/0                                                     | G/0            | <b>A/0</b>  | $\mathbf{A}/0$ |  |  |  |

| H             | <b>B</b> /1                                             | <b>D</b> /0    | <b>E</b> /1 | <b>A/0</b>     |  |  |  |

| $S_{n+1}/Z_n$ |                                                         |                |             |                |  |  |  |

The equivalent states: [A, F], [B, H], [B, C], [C, H].

Denoted by A rour Denoted by B

e ivalent state

[A, F], [B, C, H], [D], [E], [G]

| $S_n$   | 00          | 01             | 11          | 10          |

|---------|-------------|----------------|-------------|-------------|

| A       | <b>D</b> /0 | <b>D</b> /0    | <b>A/0</b>  | <b>A</b> /0 |

| В       | <b>C</b> /1 | $\mathbf{D}/0$ | <b>E</b> /1 | <b>A</b> /0 |

| D       | <b>D</b> /0 | <b>B</b> /0    | <b>A/0</b>  | <b>A</b> /0 |

| ${f E}$ | <b>B</b> /1 | <b>A</b> /0    | <b>E</b> /1 | <b>A</b> /0 |

| G       | <b>G</b> /0 | <b>G</b> /0    | <b>A</b> /0 | <b>A/0</b>  |

$$S_{n+1}/Z_n$$

| 3     | ×               |          |                 | Co       | mbi             | ned             |    |

|-------|-----------------|----------|-----------------|----------|-----------------|-----------------|----|

| 7)    | ×               | AF       |                 |          |                 | <b>,C,F</b>     | I] |

| )     | BD<br>AF        | ×        | ×               |          |                 |                 |    |

| $\Xi$ | ×               | DF<br>AF | DF <sub>×</sub> | ×        |                 |                 |    |

| F     | <b>√</b>        | ×        | ×               | BD×      | ×               |                 |    |

| 7     | DG <sub>X</sub> | ×        | ×               | BG<br>AF | ×               | DG <sub>×</sub> |    |

| I     | ×               | BC<br>AF | BC              | ×        | BC <sub>×</sub> | ×               | ×  |

|       | A               | В        | C               | D        | E               | F               | G  |

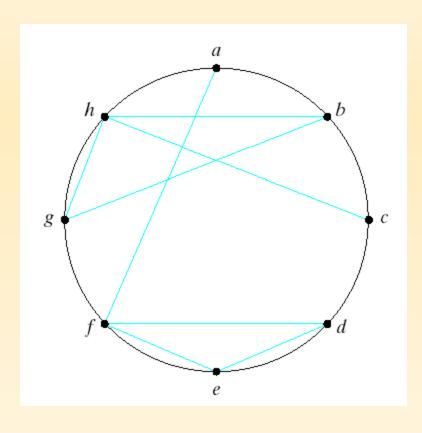

The primary objective in choosing a proper binary state assignment is the prevention of critical races.

Critical races can be avoided by making a binary state assignment in such a way that only one variable changes at any given time when a state transition occurs in the flow table.

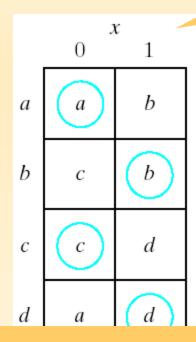

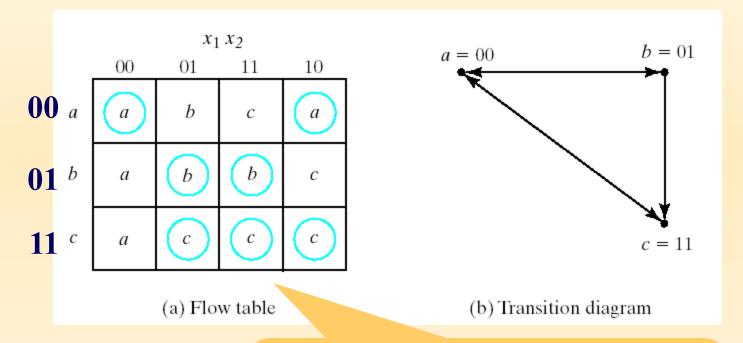

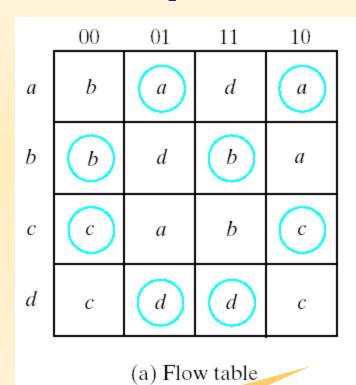

#### **Three-Row Flow-Table Example**

This assignment will cause a critical race during the transition from *a* to *c*.

#### **Three-Row Flow-Table Example**

(a) Flow table

The transition from *a* to *c* must now go through *d*, thus avoiding a critical race.

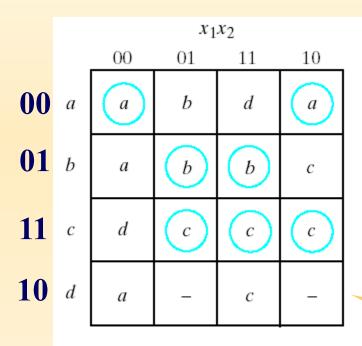

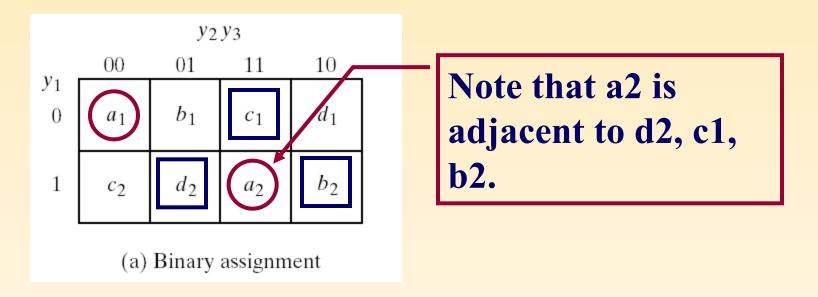

#### **Multiple-Row Method**

In the multiple-row assignment, each state in the original flow table is replaced by two or more combinations of state variables.

#### **Multiple-Row Method**

$000 = a_1$  $b_1$  $d_1$  $a_1$  $a_1$  $111 = a_2$  $d_2$  $b_2$  $a_2$  $a_2$  $d_2$  $b_1$  $001 = b_1$  $a_1$  $110 = b_2$  $b_2$  $d_1$  $b_2$  $a_2$  $011 = c_1$  $b_1$  $a_2$  $c_1$  $100 = c_2$  $b_2$  $c_2$  $a_1$  $c_2$  $d_1$  $d_1$  $010 = d_1$  $c_1$  $c_1$  $d_2$  $d_2$  $101 = d_2$  $c_2$  $c_2$

01

11

10

00

The original flow table

(b) Flow table

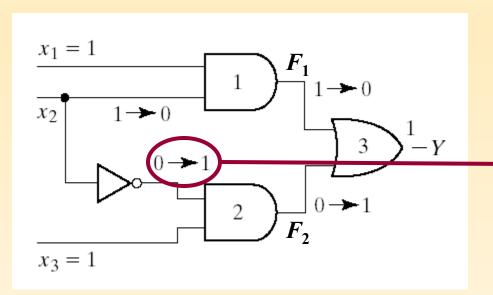

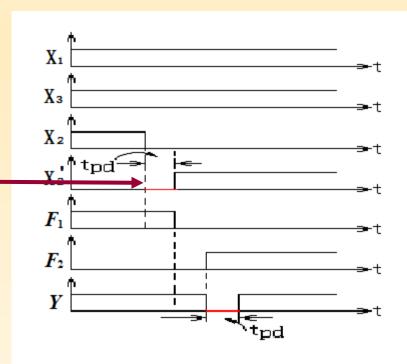

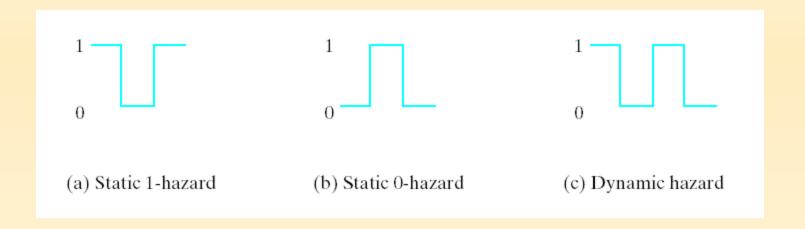

Hazards are unwanted switching transients that may appear at the output of a circuit because different paths exhibit different propagation delays.

Hazards occur in combinational circuits, where they may cause a temporary false-output value.

When hazards occur in sequential circuits, it may result in a transition to a wrong stable state.

#### **Hazards in Combinational Circuits**

#### **Hazards in Combinational Circuits**

#### **Hazards in Combinational Circuits**

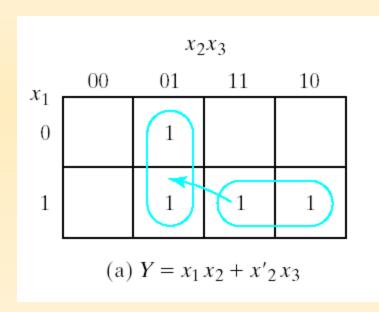

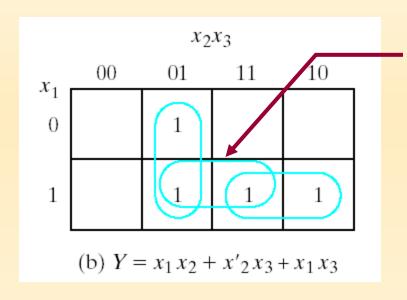

The hazard exists because the change of input results in a different product term covering the two minterms.

#### **Hazards in Combinational Circuits**

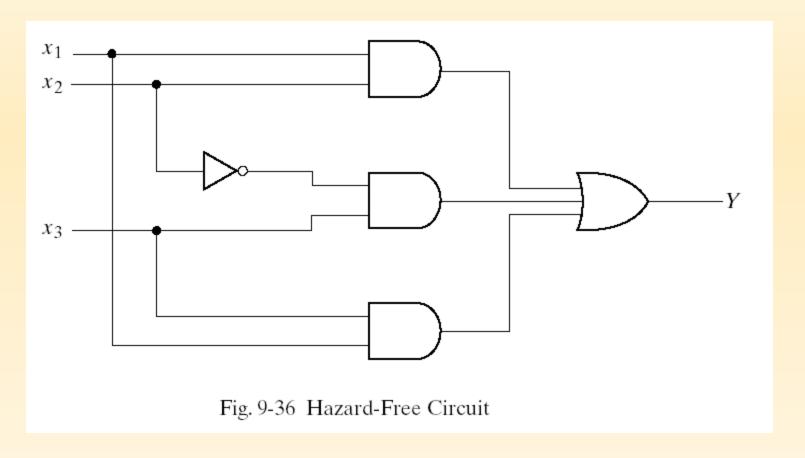

The remedy for eliminating a hazard is to enclose the two minterms in question with another product term that overlap both grouping.

#### **Hazards in Combinational Circuits**

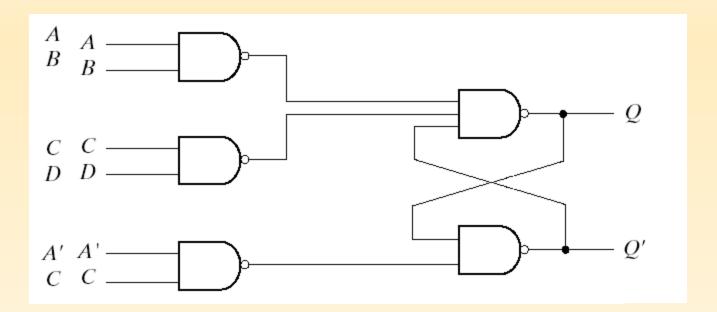

#### **Implementation with SR Latches**

Consider a NAND ST Boolean functions fo

$$S = AB + CD$$

$$R = A'C$$

$$S = (AB + CD)' = (AB)' (CD)'$$

$$R = (A'C)'$$

$$Q = (Q'S)' = [Q'(AB)'(CD)']'$$

#### **Implementation with SR Latches**

$$Q = (Q'S)' = [Q'(AB)'(CD)']'$$

#### **The Recommended Procedure**

- 1. State the design specifications

- 2. Derive a primitive flow table

- 3. Reduce the flow table by merging the rows

- 4. Make a race-free binary state assignment

- 5. Obtain the transition table and output map

- 6. Obtain the logic diagram using SR latch

#### **Design Specifications**

It is necessary to design a negative-edgetriggered flip-flop. The circuit has two inputs, T(toggle) and C (clock), and one output, Q.

#### **Primitive Flow Table**

**Specification of Total States**

|           | Inputs |   | Output |                    |

|-----------|--------|---|--------|--------------------|

| State     | 7      | C | Q      | Comments           |

| а         | 1      | 1 | 0      | Initial input is 0 |

| b         | 1      | 0 | 1      | After state a      |

| C         | 1      | 1 | 1      | Initial input is 1 |

| d         | 1      | 0 | 0      | After state c      |

| e         | 0      | 0 | 0      | After state d or f |

| f         | 0      | 1 | 0      | After state e or a |

| g         | 0      | 0 | 1      | After state b or h |

| $\bar{h}$ | 0      | 1 | 1      | After state g or c |

## **Primitive Flow Table**

|   |                | T                              | C            |                                |

|---|----------------|--------------------------------|--------------|--------------------------------|

|   | 00             | 01                             | 11           | 10                             |

| а | -,-            | f ,-                           | <b>a</b> , 0 | b ,-                           |

| b | g ,-           | -,-                            | c ,-         | <b>(</b> <i>b</i> <b>)</b> , 1 |

| С | -,-            | h ,-                           | <b>c</b> , 1 | d ,-                           |

| d | e,-            | -,-                            | a ,-         | <b>d</b> , 0                   |

| e | <b>e</b> , 0   | f ,-                           | -,-          | d ,-                           |

| f | e ,-           | <b>(</b> <i>f</i> <b>)</b> , 0 | a ,-         | -,-                            |

| g | <b>(g)</b> , 1 | h ,-                           | - ,-         | b ,-                           |

| h | g ,-           | <b>(</b> <i>h</i> <b>),</b> 1  | c ,-         | - ,-                           |

## **Design Example**

# **Primitive Flow Table**

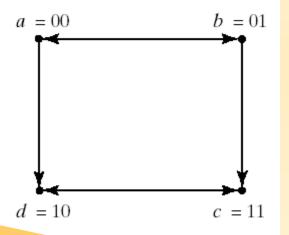

## **Implication Table**

## **Design Example**

#### $a, c \times$ $\times$ b, d $\times$ C $\times$ a, c $\times$ $b, d \times$ $b, d \times \begin{vmatrix} e, g \times \\ b, d \times \end{vmatrix} f, h \times \begin{vmatrix} e, g \times \\ b, d \times \end{vmatrix}$ $\begin{bmatrix} e, g \times & f, h \times \\ a, c \times & a, c \times \end{bmatrix}$ e, $g \times f$ , $h \times f$ $b, d \times \begin{vmatrix} e, g \times \\ b, d \times \end{vmatrix}$ $f, h \times$ Χ а g

# **Merging the Flow Table**

The compatible pairs:

#### **Merging the Flow Table**

The maximal compatible set:

$$(a, f) (b, g, h) (c, h)$$

$(d, e, f)$

#### **Merging the Flow Table**

## Reduced flow table

| TC      |                |                |                |                                |   |   | T                              | C                              |               |                               |

|---------|----------------|----------------|----------------|--------------------------------|---|---|--------------------------------|--------------------------------|---------------|-------------------------------|

|         | 00             | 01             | 11             | 10                             | - |   | 00                             | 01                             | 11            | 10                            |

| a, f    | e ,-           | <b>(f)</b> , 0 | <b>a</b> , 0   | b,-                            |   | а | d ,-                           | <b>a</b> , 0                   | <b>a</b> , 0  | <u>(b)</u> ,-                 |

| b, g, h | <b>g</b> , 1   | (h),1          | c,-            | <b>(</b> <i>b</i> <b>)</b> , 1 |   | b | <b>(</b> <i>b</i> <b>)</b> , 1 | <b>(</b> <i>b</i> <b>)</b> , 1 | c ,-          | <b>(</b> <i>b</i> <b>),</b> 1 |

| c, h    | g,1            | (h), 1         | <b>(</b> c), 1 | d ,-                           |   | c | b,-                            | <b>c</b> , 1                   | <b>(</b> c),1 | d,-                           |

| d, e, f | <b>(e)</b> , 0 | <b>(f</b> ), 0 | a,-            | (d),0                          |   | d | (d),0                          | <b>d</b> ,0                    | a , –         | <b>(d)</b> , 0                |

|         |                | (;             | a)             |                                | - | , |                                | (t                             | p)            |                               |

# **State Assignment and Transition Table**

|   | TC                   |    |    |    |    |             |       | T        | C              |                  |

|---|----------------------|----|----|----|----|-------------|-------|----------|----------------|------------------|

| а |                      | 00 | 01 | 11 | 10 |             | 00    | 01       | 11             | 10               |

| и | $y_1 y_2$ $a = 00$   | 10 | 00 | 8  | 01 | 91 92<br>00 | 0     | 0        | 0              | X                |

|   | b = 01               | 01 | 01 | 11 | 01 | 01          | 1     | 1        | 1              | 1                |

| d | <i>c</i> = 11        | 01 | 11 | 11 | 10 | 11          | 1     | 1        | 1              | X                |

|   | <i>d</i> = 10        | 10 | 10 | 00 | 10 | 10          | 0     | 0        | 0              | 0                |

|   | (a) Transition table |    |    |    |    |             | (b) ( | Output 1 | nap <i>Q</i> = | = y <sub>2</sub> |

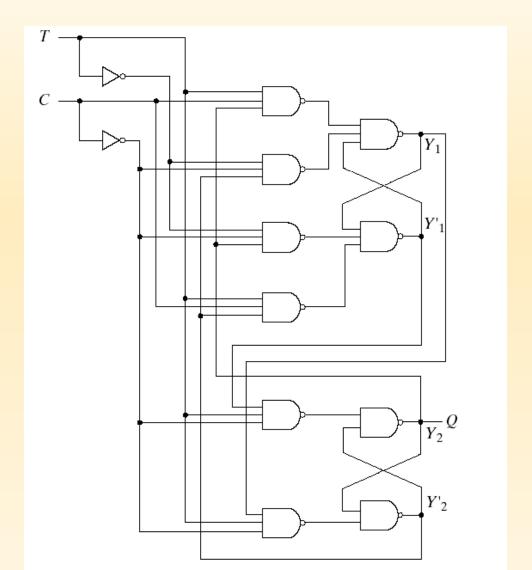

#### **Logic Diagram**

|                                             | TC |    |    |    |  |  |  |

|---------------------------------------------|----|----|----|----|--|--|--|

| <i>y</i> <sub>1</sub> <i>y</i> <sub>2</sub> | 00 | 01 | 11 | 10 |  |  |  |

| 00                                          | 1  | 0  | 0  | 0  |  |  |  |

| 01                                          | 0  | 0  | 1  | 0  |  |  |  |

| 11                                          | 0  | X  | X  | X  |  |  |  |

| 10                                          | X  | X  | 0  | X  |  |  |  |

(a)

$$S_1 = y_2 TC + y'_2 T'C'$$

|                                             | TC |    |    |    |  |  |  |  |

|---------------------------------------------|----|----|----|----|--|--|--|--|

| <i>y</i> <sub>1</sub> <i>y</i> <sub>2</sub> | 00 | 01 | 11 | 10 |  |  |  |  |

| 00                                          | 0  | 0  | 0  | 1  |  |  |  |  |

| 01                                          | X  | X  | Χ  | X  |  |  |  |  |

| 11                                          | X  | X  | Χ  | 0  |  |  |  |  |

| 10                                          | 0  | 0  | 0  | 0  |  |  |  |  |

(c)

$$S_2 = y'_1 TC'$$

|                                             | TC |    |    |    |  |  |  |  |  |

|---------------------------------------------|----|----|----|----|--|--|--|--|--|

| <i>y</i> <sub>1</sub> <i>y</i> <sub>2</sub> | 00 | 01 | 11 | 10 |  |  |  |  |  |

| 00                                          | 0  | X  | X  | X  |  |  |  |  |  |

| 01                                          | X  | Χ  | 0  | X  |  |  |  |  |  |

| 11                                          | 1  | 0  | 0  | 0  |  |  |  |  |  |

| 10                                          | 0  | 0  | 1  | 0  |  |  |  |  |  |

|                                             |    |    |    |    |  |  |  |  |  |

(b)

$$R_1 = y_2 T'C' + y'_2 TC$$

(d)

$$R_2 = y_1 TC'$$

#### **Logic Diagram**