MICROPROCESSOR ARCHITECTURE AND ITS OPERATIONS

LECTURE 2

# 8085 Microprocessor Architecture

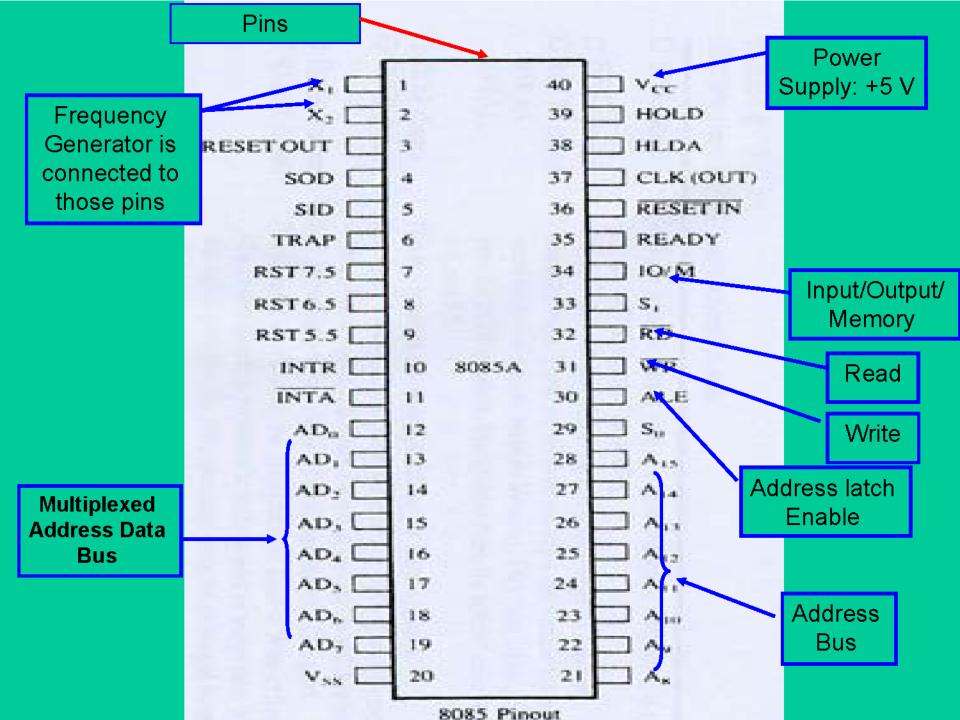

- 8-bit general purpose µp

- Capable of addressing 64 k of memory

- Has 40 pins

- Requires +5 v power supply

- Can operate with 3 MHz clock

- 8085 upward compatible

- System Bus wires connecting memory & I/O to microprocessor

- Address Bus

- Unidirectional

- Identifying peripheral or memory location

- Data Bus

- Bidirectional

- Transferring data

- Control Bus

- Synchronization signals

- Timing signals

- Control signal

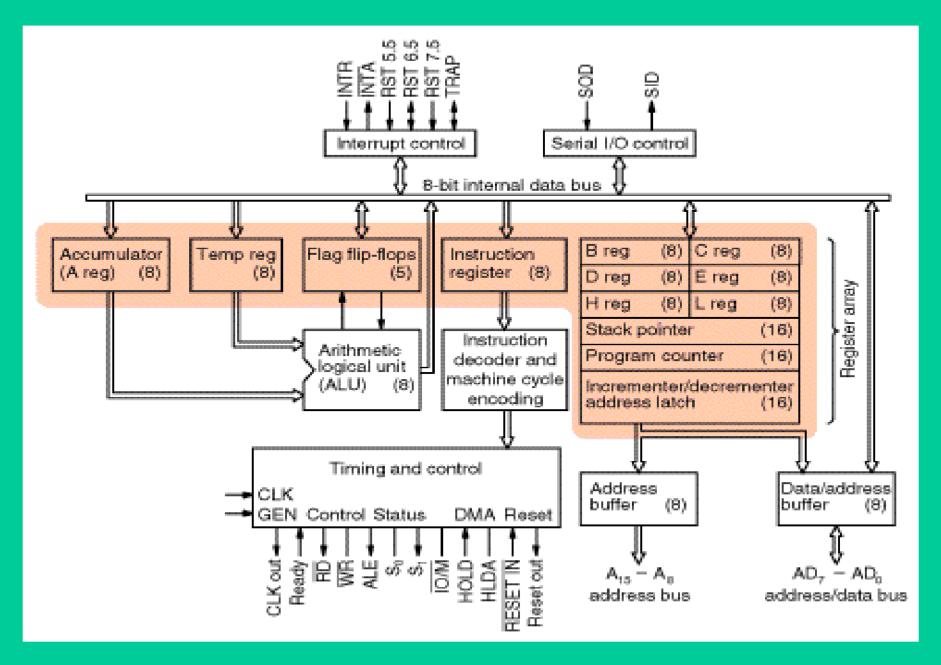

### Architecture of Intel 8085 Microprocessor

### Intel 8085 Microprocessor

- Microprocessor consists of:

- Control unit: control microprocessor operations.

- ALU: performs data processing function.

- Registers: provide storage internal to CPU.

- Interrupts

- Internal data bus

## The ALU

- In addition to the arithmetic & logic circuits, the ALU includes the accumulator, which is part of every arithmetic & logic operation.

- Also, the ALU includes a temporary register used for holding data temporarily during the execution of the operation. This temporary register is not accessible by the programmer.

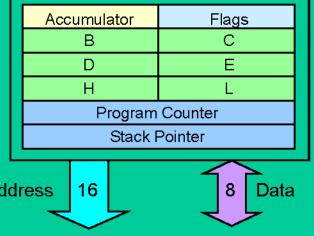

- Registers

- General Purpose Registers

- B, C, D, E, H & L (8 bit registers)

- Can be used singly

- Or can be used as 16 bit register pairs – BC, DE, HL

- H & L can be used as a data pointer (holds memory address)

- Special Purpose Registers

- Accumulator (8 bit register)

- Store 8 bit data

- Store the result of an operation

- Store 8 bit data during I/O transfer Address

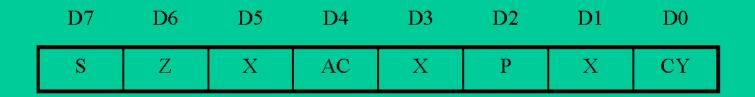

- Flag Register

- 8 bit register shows the status of the microprocessor before/after an operation

- S (sign flag), Z (zero flag), AC (auxillary carry flag), P (parity flag) & CY (carry flag)

#### - Sign Flag

- Used for indicating the sign of the data in the accumulator

- The sign flag is set if negative (1 negative)

- The sign flag is reset if positive (0 –positive)

#### Zero Flag

- Is set if result obtained after an operation is 0

- Is set following an increment or decrement operation of that register

10110011 + 01001101 \_\_\_\_\_

<u>Carry Flag</u>

- Is set if there is a carry or borrow from arithmetic operation

00000000

| Carry 1 |           | Borrow 1 |           |

|---------|-----------|----------|-----------|

| +       | 0110 1100 | -        | 1100 1100 |

|         | 1011 0101 |          | 1011 0101 |

|         |           |          |           |

<u>Auxillary Carry Flag</u>

– Is set if there is a carry out of bit 3

- <u>Parity Flag</u>

- Is set if parity is even

- Is cleared if parity is odd

## The Internal Architecture

- We have already discussed the general purpose registers, the Accumulator, and the flags.

- The Program Counter (PC)

- This is a register that is used to control the sequencing of the execution of instructions.

- This register always holds the address of the next instruction.

- Since it holds an address, it must be 16 bits wide.

## The Internal Architecture

- The Stack pointer

- The stack pointer is also a 16-bit register that is used to point into memory.

- The memory this register points to is a special area called the stack.

- The stack is an area of memory used to hold data that will be retreived soon.

- The stack is usually accessed in a Last In First Out (LIFO) fashion.

### Non Programmable Registers

- Instruction Register & Decoder

- Instruction is stored in IR after fetched by processor

- Decoder decodes instruction in IR

#### Internal Clock generator

- 3.125 MHz internally

- 6.25 MHz externally

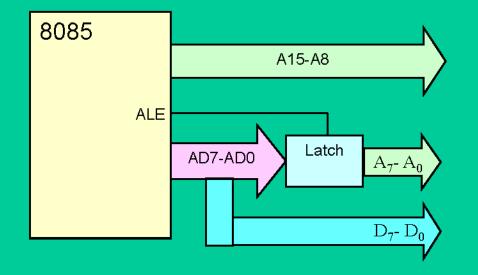

## The Address and Data Busses

- The address bus has 8 signal lines A8 A15 which are unidirectional.

- The other 8 address bits are multiplexed (time shared) with the 8 data bits.

- So, the bits AD0 AD7 are bi-directional and serve as A0 A7 and D0 D7 at the same time.

- During the execution of the instruction, these lines carry the address bits during the early part, then during the late parts of the execution, they carry the 8 data bits.

- In order to separate the address from the data, we can use a latch to save the value before the function of the bits changes.

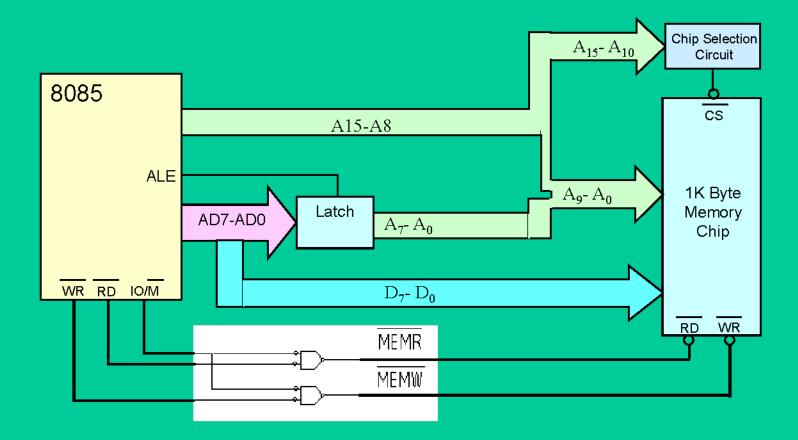

# Demultiplexing AD7-AD0

- From the above description, it becomes obvious that the AD7– AD0 lines are serving a dual purpose and that they need to be demultiplexed to get all the information.

- The high order bits of the address remain on the bus for three clock periods. However, the low order bits remain for <u>only one clock period</u> and they would be lost if they are not saved externally. Also, notice that the low order bits of the address disappear when they are needed most.

- To make sure we have the entire address for the full three clock cycles, we will use an external latch to save the value of AD7– AD0 when it is carrying the address bits. We use the ALE signal to enable this latch.

# Demultiplexing AD7-AD0

Given that ALE operates as a pulse during T1, we will be able to latch the address. Then when ALE goes low, the address is saved and the AD7– AD0 lines can be used for their purpose as the bi-directional data lines.

### Demultiplexing the Bus AD7 – AD0

- The high order address is placed on the address bus and hold for 3 clk periods,

- The low order address is lost after the first clk period, this address needs to be hold however we need to use latch

- The address AD7 AD0 is connected as inputs to the latch 74LS373.

- The ALE signal is connected to the enable (G) pin of the latch and the OC Output control of the latch is grounded

### The Overall Picture

• Putting all of the concepts together, we get: