# COUNTERS AND TIME DELAYS LECTURE 2

## Counter and Time Delays

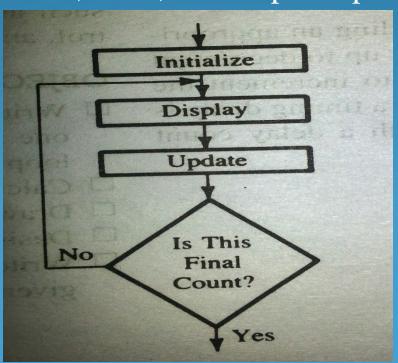

- •A counter is designed simply by loading appropriate number into one of the registers and using INR or DNR instructions.

- Loop is established to update the count.

- •Each count is checked to determine whether it has reached final number; if not, the loop is repeated.

### Time Delay

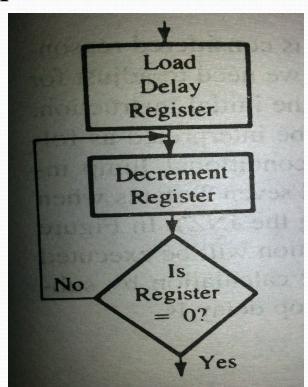

- Procedure used to design a specific delay.

- A register is loaded with a number, depending on the time delay required and then the register is decremented until it reaches zero by setting up a loop with conditional jump instruction.

- Time delay using One register:

#### Label Opcode Operand Comments T states

MVI C,FFH ;Load register C 7

LOOP: DCR C ;Decrement C 4

JNZ LOOP ;Jump back to 10/7

decrement C

Clock frequency of the system = 2 MHz

Clock period=  $1/T=0.5 \mu s$

Time to execute MVI = 7 T states \*  $0.5 = 3.5 \mu s$

Time Delay in Loop TL= T\*Loop T states \* N10 = 0.5 \* 14\* 255=  $1785 \mu s = 1.8 ms$

N<sub>10</sub> = Equivalent decimal number of hexadecimal count loaded in the delay register

TLA= Time to execute loop instructions =TL -(3T states\* clock period)=1785-1.5=1783.5 μs

#### Time Delay using a register pair

| Label | Opcode | Operand | Comments                     | T states     |

|-------|--------|---------|------------------------------|--------------|

|       | LXI    | В,2384Н | Load BC with 16-bit count    | 10           |

| LOOP: | DCX    | В       | Decrement BC by 1            | 6            |

|       | MOV    | A,C     | Place contents of C in A     | 4            |

|       | ORA    | В       | OR B with C to set Zero flag | 4            |

|       | JNZ    | LOOP    | if result not equal to 0,    | <b>10</b> /7 |

|       |        |         | jump back to loop            |              |

**Time Delay in Loop TL= T\*Loop T states \* N10**

= 0.5 \* 24\* 9092

= 109 ms

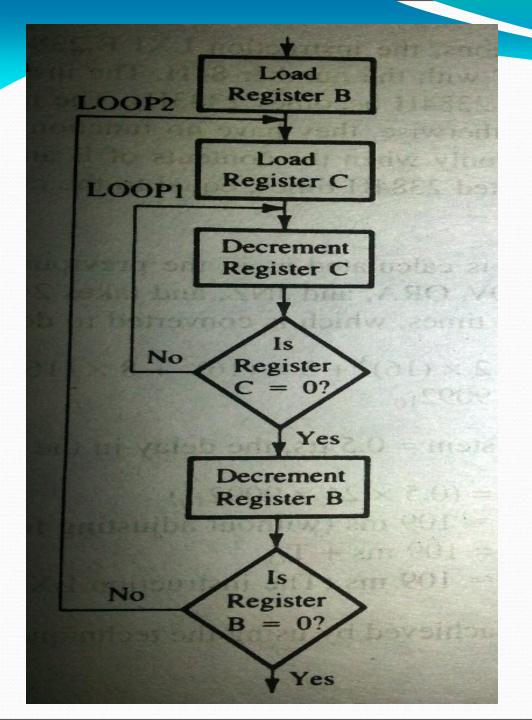

#### Time Delay using a LOOP within a LOOP

|        | MVI B,38H  | 7T            | Delay in Loop TL1=1783.5 μs          |

|--------|------------|---------------|--------------------------------------|

| LOOP2: | MVI C,FFH  | <b>7</b> T    | Delay in Loop TL2= $(0.5*21+TL1)*56$ |

| LOOP1: | DCR C      | 4T            | =100.46ms                            |

|        | JNZ LOOP1  | 10/7 T        |                                      |

|        | DCR B      | <b>4</b> T    |                                      |

|        | JNZ LOOP 2 | <b>10</b> /7T |                                      |

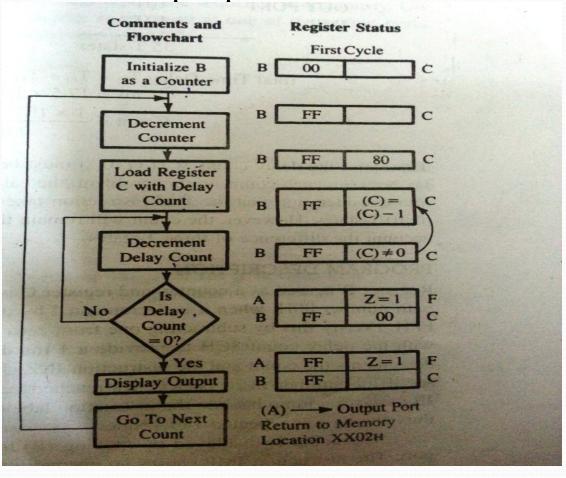

Flowchart for time delay with two loops

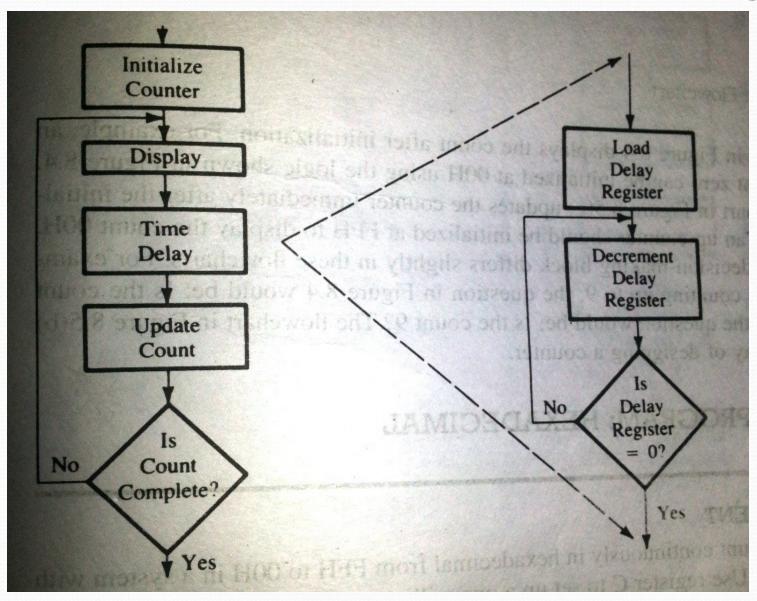

#### Flowchart of a counter with time delay

#### Illustrative Program: Hexadecimal Counter

Write a Program to count continuously from FFH to 00H using register C with delay count 8CH between each count and display the number at one of the output ports.

MVI B,00H

NEXT: DCR B

MVI C,8CH

DELAY: DCR C

JNZ DELAY

MOV A,B

**OUT PORT#**

JMP NEXT

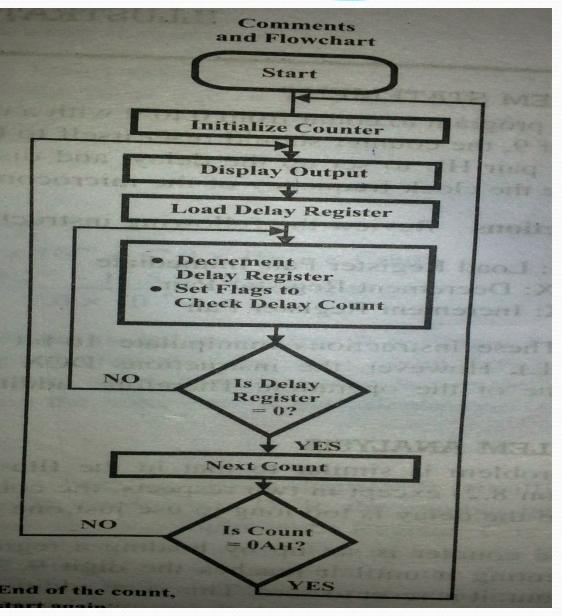

#### Illustrative Program: Zero to nine (Modulo

#### ten) Counter

START: MVI B,00H

MOV A,B

DSPLAY: OUT PORT#

LXI H,16-bit

LOOP: DCX H

MOV A,L

**ORAH**

JNZ LOOP

INR B

MOV A,B

CPI 0AH

JNZ DSPLAY

JZ START

# THANK YOU...