INTERRUPTS (Continued) LECTURE 5

# The 8085 Maskable/Vectored Interrupts

- The 8085 has 4 Masked/Vectored interrupt inputs.

RST 5.5, RST 6.5, RST 7.5

- They are all maskable.

- They are automatically vectored according to the following table:

| Interrupt | Vector |

|-----------|--------|

| RST 5.5   | 002CH  |

| RST 6.5   | 0034H  |

| RST 7.5   | 003CH  |

The vectors for these interrupt fall in between the vectors for the RST instructions. That's why they have names like RST 5.5 (RST 5 and a half).

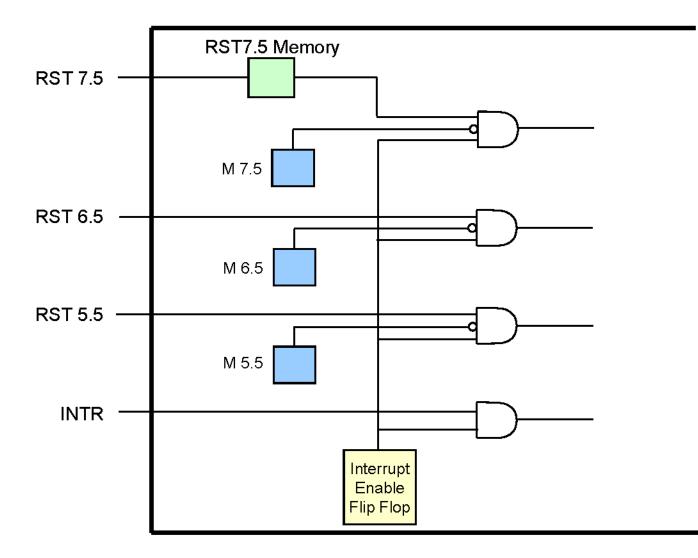

# Masking RST 5.5, RST 6.5 and RST 7.5

- These three interrupts are masked at two levels:

- Through the Interrupt Enable flip flop and the EI/DI instructions.

- The Interrupt Enable flip flop controls the whole maskable interrupt process.

- Through individual mask flip flops that control the availability of the individual interrupts.

- These flip flops control the interrupts individually.

#### Maskable Interrupts

#### The 8085 Maskable/Vectored Interrupt Process

- 1. The interrupt process should be enabled using the EI instruction.

- 2. The 8085 checks for an interrupt during the execution of every instruction.

- 3. If there is an interrupt, <u>and if the interrupt is</u> <u>enabled using the interrupt mask</u>, the microprocessor will complete the executing instruction, and reset the interrupt flip flop.

- 4. The microprocessor then executes a call instruction that sends the execution to the appropriate location in the interrupt vector table.

#### The 8085 Maskable/Vectored Interrupt Process

- 5. When the microprocessor executes the call instruction, it saves the address of the next instruction on the stack.

- 6. The microprocessor jumps to the specific service routine.

- 7. The service routine must include the instruction EI to re-enable the interrupt process.

- 8. At the end of the service routine, the RET instruction returns the execution to where the program was interrupted.

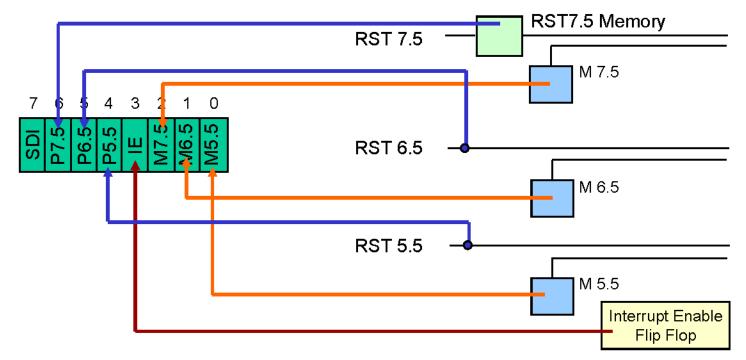

# Manipulating the Masks

- The Interrupt Enable flip flop is manipulated using the EI/DI instructions.

- The individual masks for RST 5.5, RST 6.5 and RST 7.5 are manipulated using the SIM instruction.

- This instruction takes the bit pattern in the Accumulator and applies it to the interrupt mask enabling and disabling the specific interrupts.

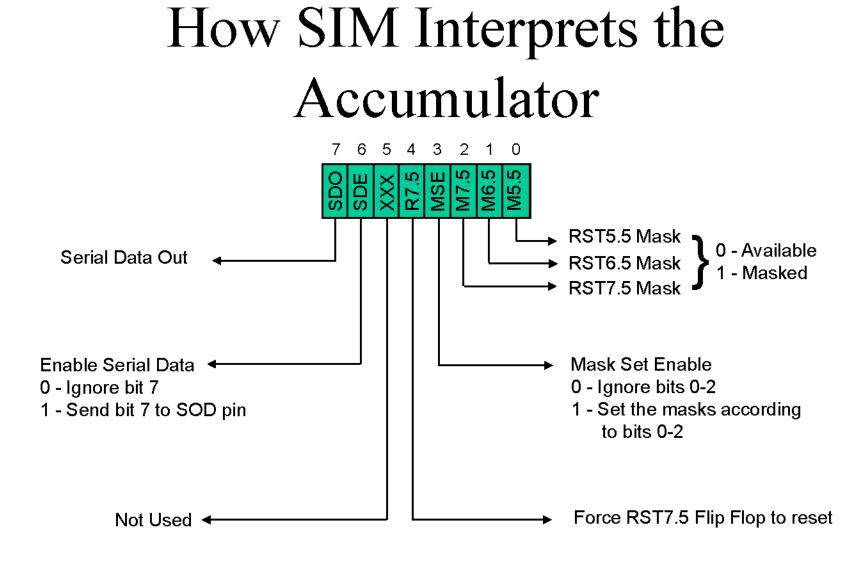

# SIM and the Interrupt Mask

- Bit 0 is the mask for RST 5.5, bit 1 is the mask for RST 6.5 and bit 2 is the mask for RST 7.5.

- If the mask bit is 0, the interrupt is available.

- If the mask bit is 1, the interrupt is masked.

- Bit 3 (Mask Set Enable MSE) is an enable for setting the mask.

- If it is set to 0 the mask is ignored and the old settings remain.

- If it is set to 1, the new setting are applied.

- The SIM instruction is used for multiple purposes and not only for setting interrupt masks.

- It is also used to control functionality such as Serial Data Transmission.

- Therefore, bit 3 is necessary to tell the microprocessor whether or not the interrupt masks should be modified

#### SIM and the Interrupt Mask

- The RST 7.5 interrupt is the only 8085 interrupt that has memory.

- If a signal on RST7.5 arrives while it is masked, a flip flop will remember the signal.

- When RST7.5 is unmasked, the microprocessor will be interrupted even if the device has removed the interrupt signal.

- This flip flop will be automatically reset when the microprocessor responds to an RST 7.5 interrupt.

- Bit 4 of the accumulator in the SIM instruction allows explicitly resetting the RST 7.5 memory even if the microprocessor did not respond to it.

# SIM and the Interrupt Mask

- The SIM instruction can also be used to perform serial data transmission out of the 8085's SOD pin.

- One bit at a time can be sent out serially over the SOD pin.

- Bit 6 is used to tell the microprocessor whether or not to perform serial data transmission

- If 0, then do not perform serial data transmission

- If 1, then do.

- The value to be sent out on SOD has to be placed in bit 7 of the accumulator.

- Bit 5 is not used by the SIM instruction

#### Using the SIM Instruction to Modify the Interrupt Masks

• Example: Set the interrupt masks so that RST5.5 is enabled, RST6.5 is masked, and RST7.5 is enabled.

- First, determine the contents of the accumulator

- Enable 5.5 bit 0 = 0- Disable 6.5 bit 1 = 1- Enable 7.5 bit 2 = 0- Allow setting the masks bit 3 = 1- Don't reset the flip flop bit 4 = 0- Bit 5 is not used bit 5 = 0- Don't use serial data bit 6 = 0- Serial data is ignored bit 7 = 0

| SDO | SDE | XXX | R7.5 | MSE | M7.5 | M6.5 | M5.5 |

|-----|-----|-----|------|-----|------|------|------|

| 0   | 0   | 0   | 0    | 1   | 0    | 1    | 0    |

Contents of accumulator are: 0AH

| El        | ; Enable interrupts including INTR                         |

|-----------|------------------------------------------------------------|

| MVI A, 0A | ; Prepare the mask to enable RST 7.5, and 5.5, disable 6.5 |

| SIM       | ; Apply the settings RST masks                             |

# Triggering Levels

- RST 7.5 is positive edge sensitive.

- When a positive edge appears on the RST7.5 line, a logic 1 is stored in the flip-flop as a "pending" interrupt.

- Since the value has been stored in the flip flop, the line does not have to be high when the microprocessor checks for the interrupt to be recognized.

- The line must go to zero and back to one before a new interrupt is recognized.

- RST 6.5 and RST 5.5 are level sensitive.

- The interrupting signal must remain present until the microprocessor checks for interrupts.

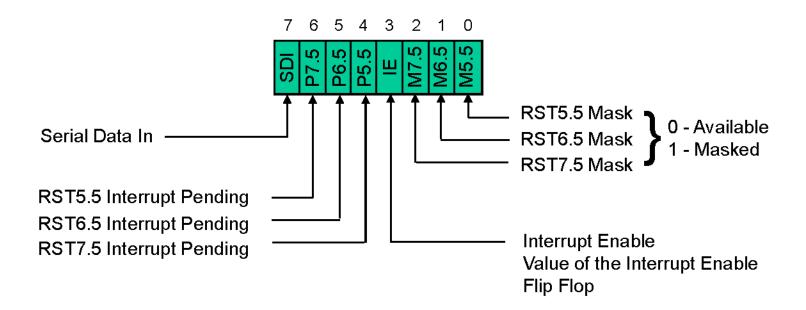

# Determining the Current Mask Settings

- RIM instruction: Read Interrupt Mask

- Load the accumulator with an 8-bit pattern showing the status of each interrupt pin and mask.

# How RIM sets the Accumulator's different bits

# The RIM Instruction and the Masks

- Bits 0-2 show the current setting of the mask for each of RST 7.5, RST 6.5 and RST 5.5

- They return the contents of the three mask flip flops.

- They can be used by a program to read the mask settings in order to modify only the right mask.

- Bit 3 shows whether the maskable interrupt process is enabled or not.

- It returns the contents of the Interrupt Enable Flip Flop.

- It can be used by a program to determine whether or not interrupts are enabled.

# The RIM Instruction and the Masks

- Bits 4-6 show whether or not there are pending interrupts on RST 7.5, RST 6.5, and RST 5.5

- Bits 4 and 5 return the current value of the RST5.5 and RST6.5 pins.

- Bit 6 returns the current value of the RST7.5 memory flip flop.

- Bit 7 is used for Serial Data Input.

- The RIM instruction reads the value of the SID pin on the microprocessor and returns it in this bit.

### Pending Interrupts

- Since the 8085 has five interrupt lines, interrupts may occur during an ISR and remain pending.

- Using the RIM instruction, the programmer can read the status of the interrupt lines and find if there are any pending interrupts.

- The advantage is being able to find about interrupts on RST 7.5, RST 6.5, and RST 5.5 without having to enable low level interrupts like INTR.

# Using RIM and SIM to set Individual Masks

- Example: Set the mask to enable RST6.5 without modifying the masks for RST5.5 and RST7.5.

- In order to do this correctly, we need to use the RIM instruction to find the current settings of the RST5.5 and RST7.5 masks.

- Then we can use the SIM instruction to set the masks using this information.

- Given that both RIM and SIM use the Accumulator, we can use some logical operations to masks the un-needed values returned by RIM and turn them into the values needed by SIM.

# Using RIM and SIM to set Individual Masks

– Assume the RST5.5 and RST7.5 are enabled and the interrupt process is disabled. Accumulator SDI P7.5 P6.5 P5.5 IE M6. M5. ЧZ RIM ; Read the current settings. ORI 08H ;00001000 0 0 0 1 Ó 1 ; Set bit 4 for MSE. ANI 0DH ;00001101 0 0 0 0 1 0 ; Turn off Serial Data, Don't reset ; RST7.5 flip flop, and set the mask ; for RST6.5 off. Don't cares are ; assumed to be 0. SIM ; Apply the settings. SDC SDE XXX R7.5 MSE M6.5 M5.5

#### TRAP

- TRAP is the only non-maskable interrupt.

- It does not need to be enabled because it cannot be disabled.

- It has the highest priority amongst interrupts.

- It is edge and level sensitive.

- It needs to be high and stay high to be recognized.

- Once it is recognized, it won't be recognized again until it goes low, then high again.

- TRAP is usually used for power failure and emergency shutoff.

## Internal Interrupt Priority

- Internally, the 8085 implements an interrupt priority scheme.

- The interrupts are ordered as follows:

- TRAP

- RST 7.5

- RST 6.5

- RST 5.5

- INTR

However, TRAP has lower priority than the HLD signal used for DMA.

#### The 8085 Interrupts

| Interrupt<br>Name    | Maskable | Masking<br>Method           | Vectored | Memory | Triggerin<br>g Method        |

|----------------------|----------|-----------------------------|----------|--------|------------------------------|

| INTR                 | Yes      | DI / EI                     | No       | No     | Level<br>Sensitive           |

| RST 5.5 /<br>RST 6.5 | Yes      | DI / EI<br><mark>SIM</mark> | Yes      | No     | Level<br>Sensitive           |

| RST 7.5              | Yes      | DI / EI<br><mark>SIM</mark> | Yes      | Yes    | Edge<br>Sensitive            |

| TRAP                 | No       | None                        | Yes      | No     | Level &<br>Edge<br>Sensitive |