## Magnitude Comparator, Decoders & Encoders Lecture 3

Dronacharya Group of Institutions

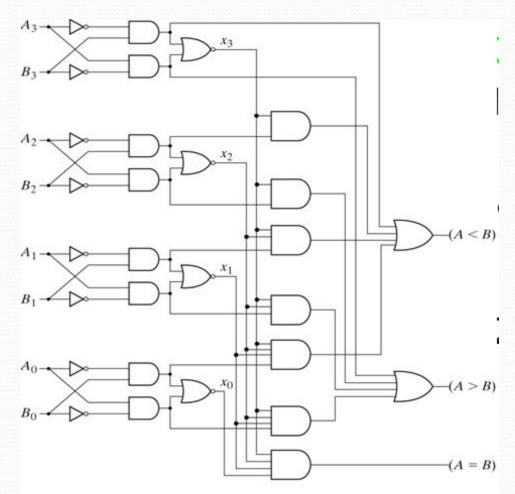

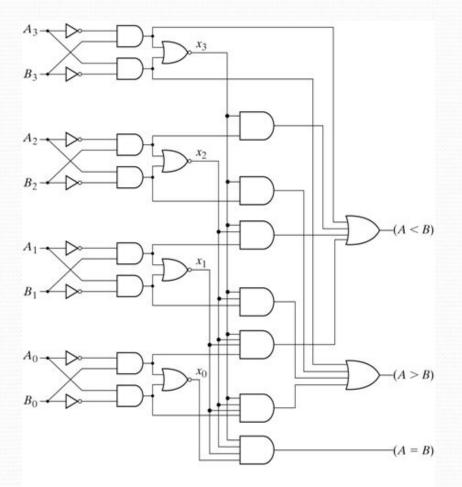

## Magnitude comparator

• The equality relation of each pair of bits can be expressed logically with an exclusive-NOR function as:

$$A = A_{3}A_{2}A_{1}A_{0}; B = B_{3}B_{2}B_{1}B_{0}$$

$$x_{i}=A_{i}B_{i}+A_{i}'B_{i}' \qquad \text{for } i = 0, 1, 2, 3$$

$$(\mathbf{A} = \mathbf{B}) = \mathbf{x}_3 \mathbf{x}_2 \mathbf{x}_1 \mathbf{x}_0$$

4-Bit Magnitude Comparator

## Magnitude comparator

- We inspect the relative magnitudes of pairs of MSB. If equal, we compare the next lower significant pair of digits until a pair of unequal digits is reached.

- If the corresponding digit of A is 1 and that of B is o, we conclude that A>B.

- $(A>B)=A_{3}B'_{3}+x_{3}A_{2}B'_{2}+x_{3}x_{2}A_{1}B'_{1}+x_{3}x_{2}x_{1}$   $A_{0}B'_{0}$   $(A<B)=A'_{3}B_{3}+x_{3}A'_{2}B_{2}+x_{3}x_{2}A'_{1}B_{1}+x_{3}x_{2}x_{1}$  $A'_{0}B_{0}$

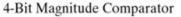

## Decoders

- The decoder is called n-to-m-line decoder, where m≤2<sup>n</sup>.

- the decoder is also used in conjunction with other code converters such as a BCD-to-seven\_segment decoder.

- 3-to-8 line decoder: For each possible input combination, there are seven outputs that are equal to 0 and only one that is equal to 1.

#### Implementation and truth table

| Inputs |   |   |                |       |       | Out   | outs  |       |       |                |

|--------|---|---|----------------|-------|-------|-------|-------|-------|-------|----------------|

| х      | У | z | D <sub>0</sub> | $D_1$ | $D_2$ | $D_3$ | $D_4$ | $D_5$ | $D_6$ | D <sub>7</sub> |

| 0      | 0 | 0 | 1              | 0     | 0     | 0     | 0     | 0     | 0     | 0              |

| 0      | 0 | 1 | 0              | 1     | 0     | 0     | 0     | 0     | 0     | 0              |

| 0      | 1 | 0 | 0              | 0     | 1     | 0     | 0     | 0     | 0     | 0              |

| 0      | 1 | 1 | 0              | 0     | 0     | 1     | 0     | 0     | 0     | 0              |

| 1      | 0 | 0 | 0              | 0     | 0     | 0     | 1     | 0     | 0     | 0              |

| 1      | 0 | 1 | 0              | 0     | 0     | 0     | 0     | 1     | 0     | 0              |

| 1      | 1 | 0 | 0              | 0     | 0     | 0     | 0     | 0     | 1     | 0              |

| 1      | 1 | 1 | 0              | 0     | 0     | 0     | 0     | 0     | 0     | 1              |

3-to-8-Line Decoder

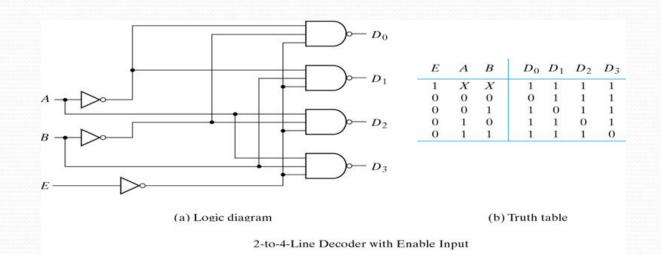

## Decoder with enable input

- Some decoders are constructed with NAND gates, it becomes more economical to generate the decoder minterms in their complemented form.

- As indicated by the truth table , only one output can be equal to 0 at any given time, all other outputs are equal to 1.

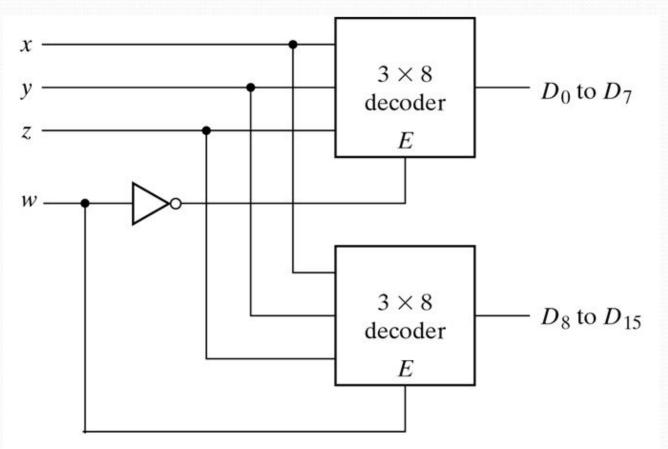

# 3-to-8 decoder with enable implement the 4-to-16 decoder

$4 \times 16$  Decoder Constructed with Two  $3 \times 8$  Decoders

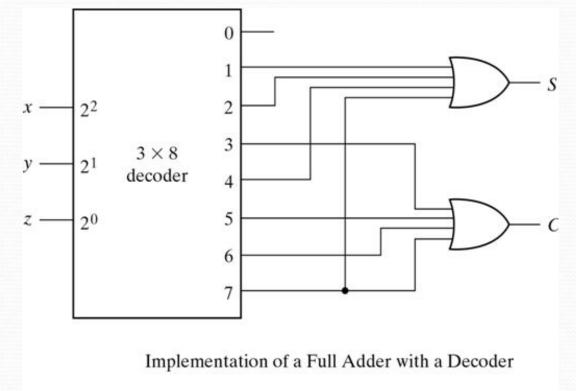

### Implementation of a Full Adder with a Decoder

• From table 4-4, we obtain the functions for the combinational circuit in sum of minterms:

$$S(x, y, z) = \sum(1, 2, 4, 7)$$

C(x, y, z) =  $\sum(3, 5, 6, 7)$

## Encoders

- An encoder is the inverse operation of a decoder.

- We can derive the Boolean functions by table 4-7

$z = D_1 + D_3 + D_5 + D_7$  $y = D_2 + D_3 + D_6 + D_7$  $x = D_4 + D_5 + D_6 + D_7$

| Inputs |       |       |       |       |       |       | Outputs |   |   |   |

|--------|-------|-------|-------|-------|-------|-------|---------|---|---|---|

| $D_0$  | $D_1$ | $D_2$ | $D_3$ | $D_4$ | $D_5$ | $D_6$ | $D_7$   | x | У | z |

| 1      | 0     | 0     | 0     | 0     | 0     | 0     | 0       | 0 | 0 | 0 |

| 0      | 1     | 0     | 0     | 0     | 0     | 0     | 0       | 0 | 0 | 1 |

| 0      | 0     | 1     | 0     | 0     | 0     | 0     | 0       | 0 | 1 | 0 |

| 0      | 0     | 0     | 1     | 0     | 0     | 0     | 0       | 0 | 1 | 1 |

| 0      | 0     | 0     | 0     | 1     | 0     | 0     | 0       | 1 | 0 | 0 |

| 0      | 0     | 0     | 0     | 0     | 1     | 0     | 0       | 1 | 0 | 1 |

| 0      | 0     | 0     | 0     | 0     | 0     | 1     | 0       | 1 | 1 | 0 |

| 0      | 0     | 0     | 0     | 0     | 0     | 0     | 1       | 1 | 1 | 1 |

## **Priority encoder**

- If two inputs are active simultaneously, the output produces an undefined combination. We can establish an input priority to ensure that only one input is encoded.

- Another ambiguity in the octal-to-binary encoder is that an output with all o's is generated when all the inputs are o; the output is the same as when D<sub>o</sub> is equal to 1.

- The discrepancy tables on Table 4-7 and Table 4-8 can resolve aforesaid condition by providing one more output to indicate that at least one input is equal to 1.

## Priority encoder

#### V=o→no valid inputs V=1→valid inputs

X's in output columns represent don't-care conditions X's in the input columns are useful for representing a truth table in condensed form. Instead of listing all 16 minterms of four variables.

#### Truth Table of a Priority Encoder

|    | Inp | uts            | Outputs        |   |   |   |

|----|-----|----------------|----------------|---|---|---|

| Do | D1  | D <sub>2</sub> | D <sub>3</sub> | x | y | V |

| 0  | 0   | 0              | 0              | X | X | 0 |

| 1  | 0   | 0              | 0              | 0 | 0 | 1 |

| X  | 1   | 0              | 0              | 0 | 1 | 1 |

| X  | X   | 1              | 0              | 1 | 0 | 1 |

| X  | X   | X              | 1              | 1 | 1 | 1 |

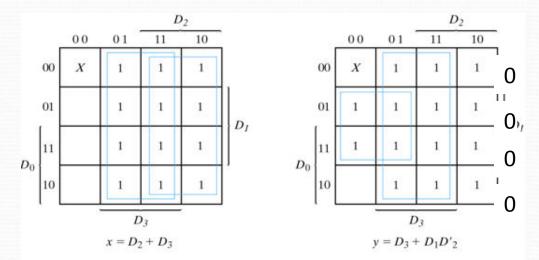

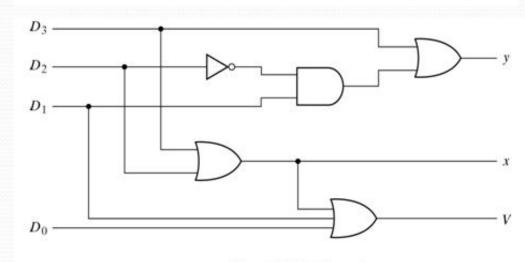

## 4-input priority encoder

Implementation:

$x = D_{2} + D_{3}$   $y = D_{3} + D_{1}D'_{2}$  $V = D_{0} + D_{1} + D_{2} + D_{3}$

Maps for a Priority Encoder

<sup>4-</sup>Input Priority Encoder