### **Asynchronous Sequential Logic**

#### **LECTURE 4**

**Dronacharya Group of Institutions**

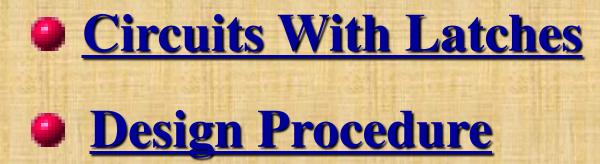

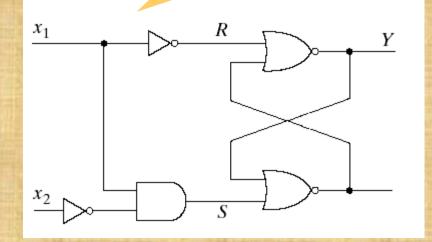

#### SR Latch

# The circuit diagram and truth table of the SR latch are shown as follows,

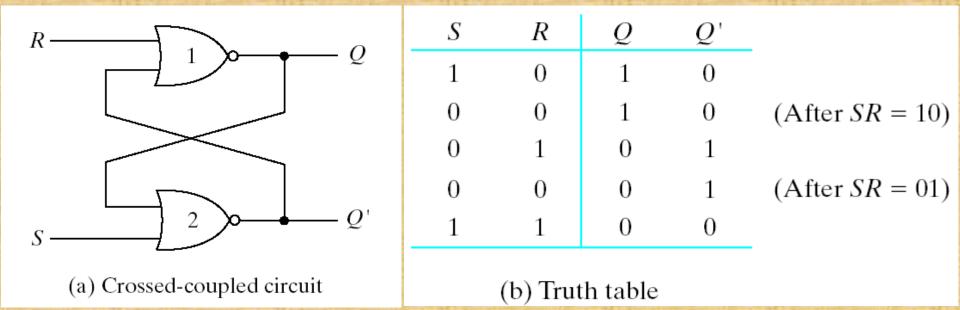

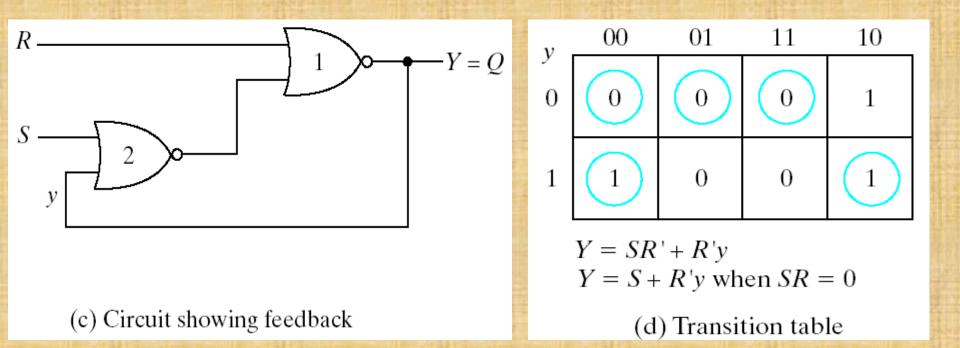

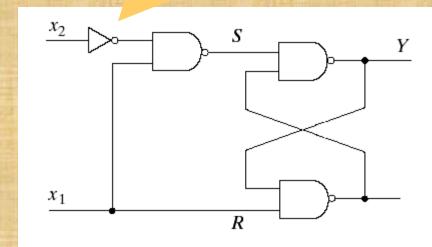

#### SR Latch

# The circuit diagram of the SR latch can be redrawn as follows,

SR Latch Y = [(S + y)' + R]' = (S + y)R' = SR' + R'y SR' + SR = S(R' + R) = S SR = 0 SR' = S

$Y = SR' + R'y = S + R'y \quad \text{when } SR = 0$

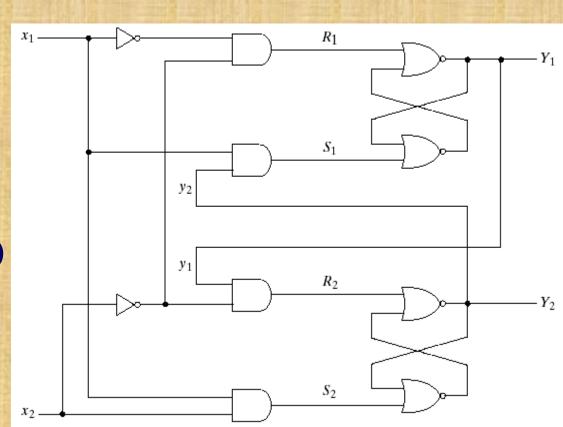

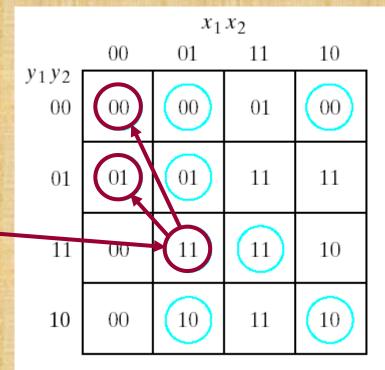

#### **Analysis Example**

$S_1 = x_1 y_2$  $S_2 = x_1 x_2$  $R_1 = x'_1 x'_2$  $R_2 = x'_2 y_1$  $S_1 R_1 = x_1 y_2 x'_1 x'_2 = 0$  $S_2 R_2 = x_1 x_2 x'_2 y_1 = 0$

#### **Analysis Example**

$$Y_1 = S_1 + R'_1 y_1 = x_1 y_2 + (x_1 + x_2) y_1$$

$$Y_2 = S_2 + R'_2 y_2 = x_1 x_2 + (x_2 + y'_1) y_2$$

There is a critical race condition

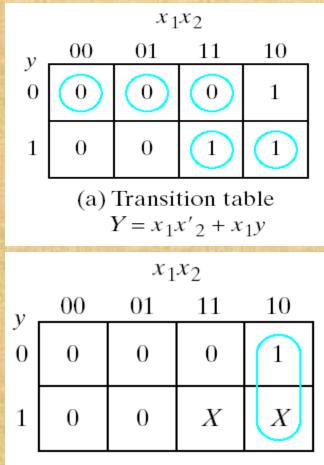

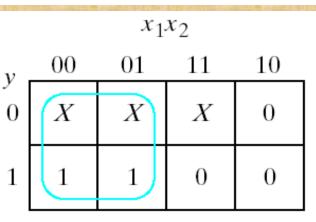

### **Latch Excitation Table**

A table that lists the required inputs *S* and **R** for each of the possible transitions from *y* to *Y*

The first two columns list the four possible transitions from y to Y.

| у | Y | S | R |

|---|---|---|---|

| 0 | 0 | 0 | X |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | X | 1 |

(b) Latch excitation table

The next two columns specify the required input values that will result in the specified transition.

#### **Implementation Example**

| (c) Map | for | <i>S</i> = | $x_1 x'_2$ |  |

|---------|-----|------------|------------|--|

|---------|-----|------------|------------|--|

| У | Y | S | R |

|---|---|---|---|

| 0 | 0 | 0 | X |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | X | 1 |

(b) Latch excitation table

(d) Map for  $R = x'_1$

### **Implementation Example**

$S = x_1 x'_2 \qquad R = x'_1$

#### Circuit with NOR latch

#### **Circuit with** NAND latch

### **Design Example**

Design a gated latch circuit with two inputs G (gate) and D (data), and one output Q. Gated-Latch

| Inputs |   | Output | Total Stat |                                  |

|--------|---|--------|------------|----------------------------------|

| State  | D | G      | Q          | comments                         |

| a      | 0 | 1      | 0          | D = Q because $G = 1$            |

| b      | 1 | 1      | 1          | D = Q because $G = 1$            |

| С      | 0 | 0      | 0          | After state <i>a</i> or <i>d</i> |

| d      | 1 | 0      | 0          | After state c                    |

| е      | 1 | 0      | 1          | After state b or f               |

| f      | 0 | 0      | 1          | After state e                    |

#### **Design Example**

|       | Inputs |   | Output |  |

|-------|--------|---|--------|--|

| State | D      | G | Q      |  |

| а     | 0      | 1 | 0      |  |

| b     | 1      | 1 | 1      |  |

| С     | 0      | 0 | 0      |  |

| d     | 1      | 0 | 0      |  |

| е     | 1      | 0 | 1      |  |

| f     | 0      | 0 | 1      |  |

Two of more rows in the primitive flow table can be merged into one row if there are non-conflicting states and outputs in each of the columns.

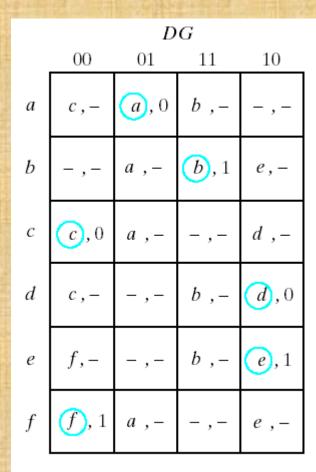

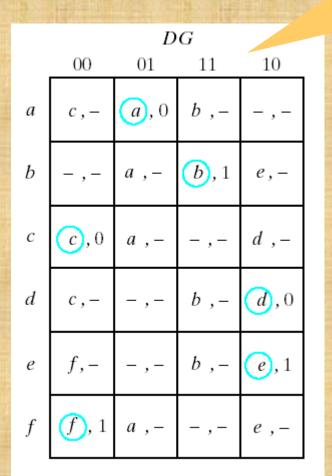

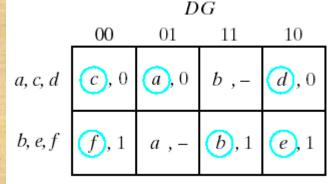

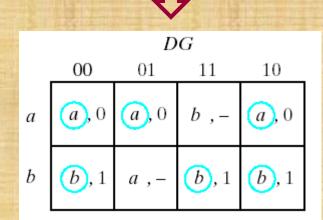

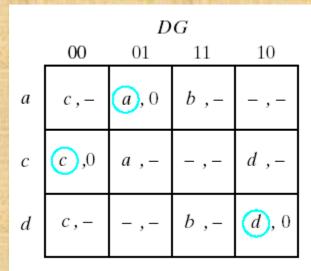

#### **Reduction of the Primitive Flow** Table

|                   | DG             |              |                      |                  |  |  |  |

|-------------------|----------------|--------------|----------------------|------------------|--|--|--|

|                   | 00             | 01           | 11                   | 10               |  |  |  |

| а                 | с,-            | <b>a</b> , 0 | b ,-                 | - ,-             |  |  |  |

| с                 | <b>c</b> ,0    | a ,-         | - ,-                 | d ,-             |  |  |  |

| d                 | с,-            | - ,-         | b ,-                 | <b>(d)</b> , 0   |  |  |  |

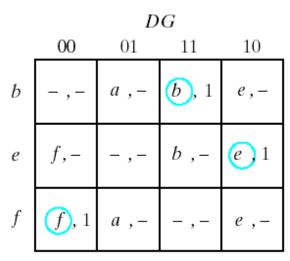

| DG<br>00 01 11 10 |                |              |                      |                  |  |  |  |

|                   |                | 01           | 11                   | 10               |  |  |  |

| b                 | - ,-           | a ,-         | <mark>(b)</mark> , 1 | e , –            |  |  |  |

| е                 | f,-            | - ,-         | b ,-                 | <mark>@</mark> 1 |  |  |  |

| f                 | <b>(f)</b> , 1 | a ,-         | - ,-                 | e ,-             |  |  |  |

### **Reduction of the Primitive Flow Table**

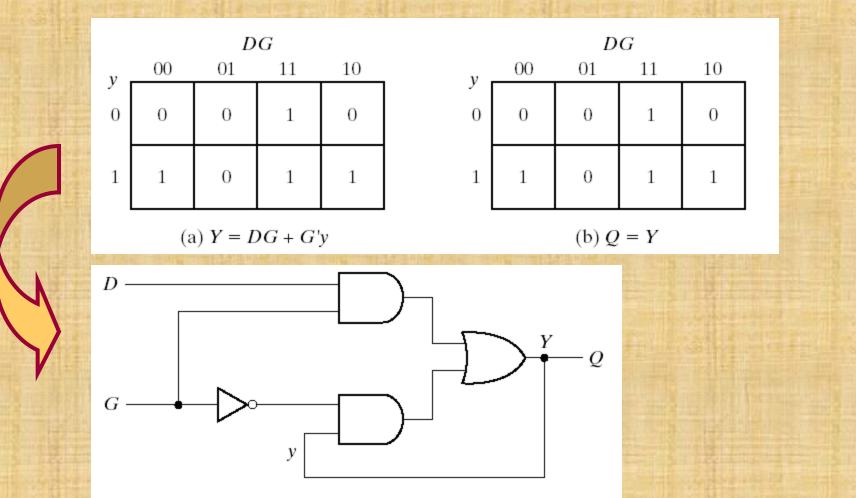

#### **Transition Table and Logic Diagram**

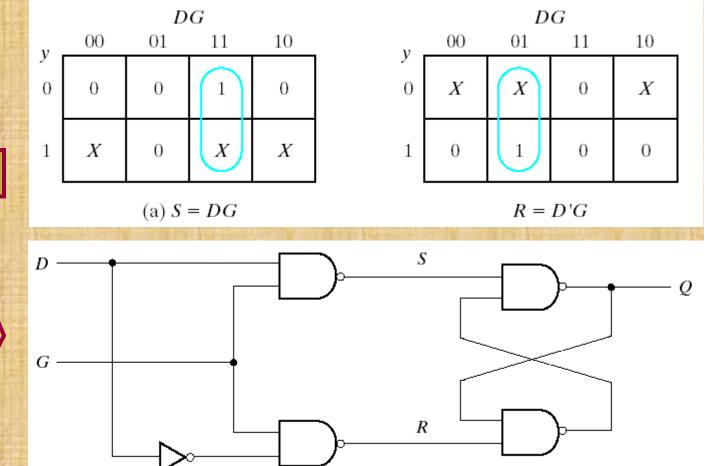

### **Circuit With SR Latch**

#### **Assigning Output to Unstable States**

- 1. Assign a 0 to an output variable associated with an unstable state that is a transient state between two stable states that have a 0 in the corresponding output variable.

- 2. Assign a 1 to an output variable associated with an unstable state that is a transient state between two stable states that have a 1 in the corresponding output variable.

- 3. Assign a don't-care condition to an output variable associated with an unstable state that is a transient state between two stable states that have different values in the corresponding output variable.