# **Asynchronous Counters Lecture 3**

**Dronacharya Group of Institutions**

- Asynchronous counters: the flip-flops do not change states at exactly the same time as they do not have a common clock pulse.

- Also known as ripple counters, as the input clock pulse "ripples" through the counter – cumulative delay is a drawback.

- n flip-flops  $\rightarrow$  a MOD (modulus)  $2^n$  counter. (Note: A MOD-x counter cycles through x states.)

- Output of the last flip-flop (MSB) divides the input clock frequency by the MOD number of the counter, hence a counter is also a frequency divider.

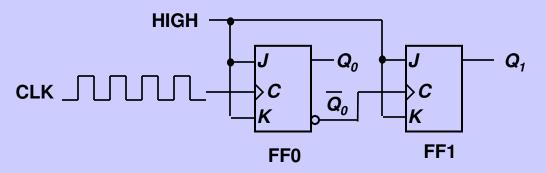

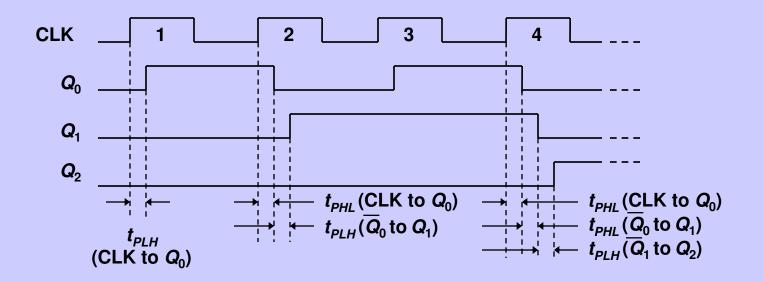

- Example: 2-bit ripple binary counter.

- Output of one flip-flop is connected to the clock input of the next more-significant flip-flop.

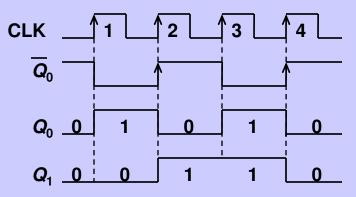

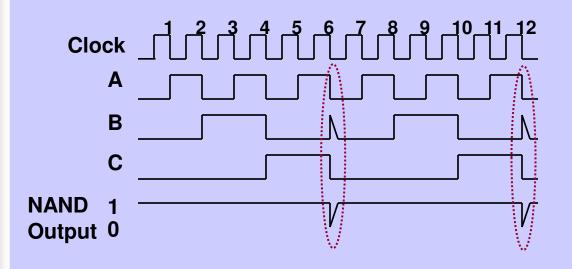

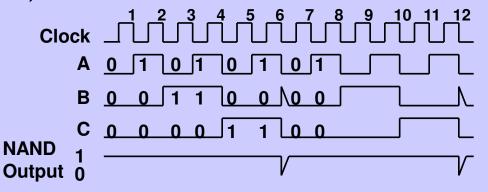

Timing diagram

$$00 \rightarrow 01 \rightarrow 10 \rightarrow 11 \rightarrow 00 \dots$$

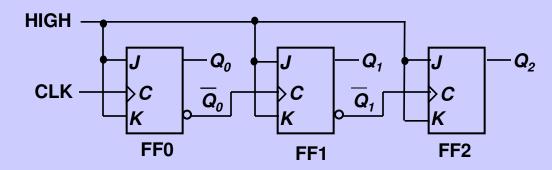

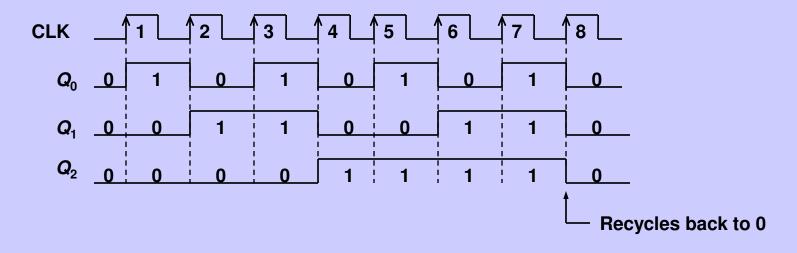

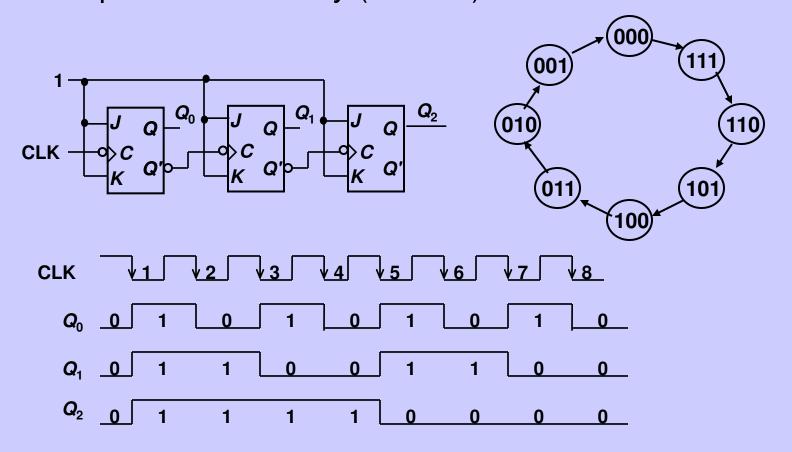

Example: 3-bit ripple binary counter.

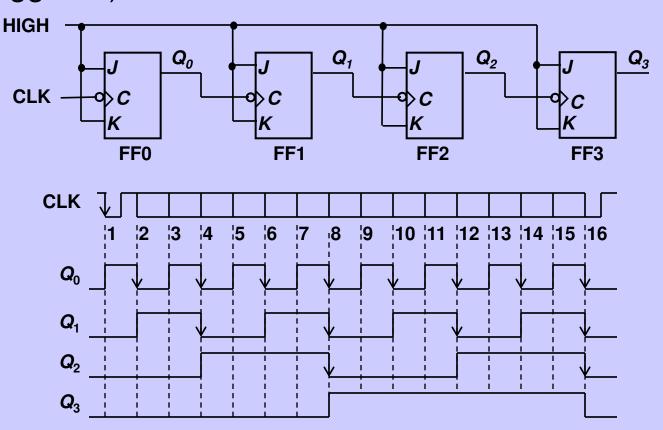

- Propagation delays in an asynchronous (rippleclocked) binary counter.

- If the accumulated delay is greater than the clock pulse, some counter states may be misrepresented!

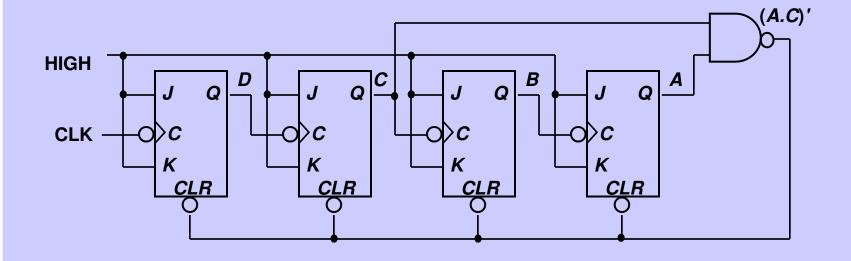

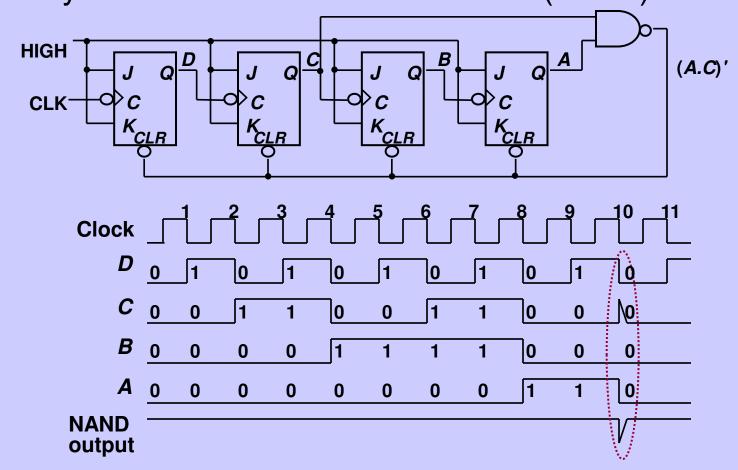

Example: 4-bit ripple binary counter (negative-edge triggered).

- States may be skipped resulting in a truncated sequence.

- Technique: force counter to recycle before going through all of the states in the binary sequence.

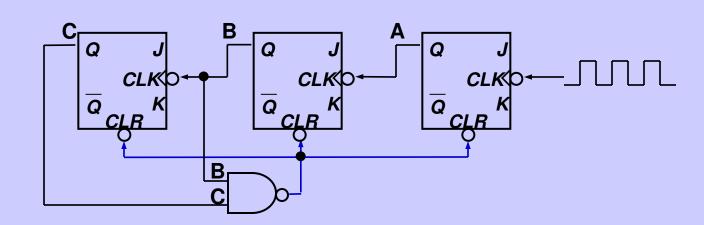

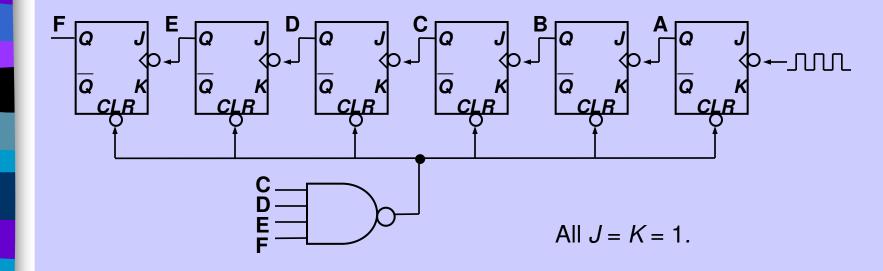

- Example: Given the following circuit, determine the counting sequence (and hence the modulus no.)

All *J*, *K* inputs are 1 (HIGH).

Example (cont'd):

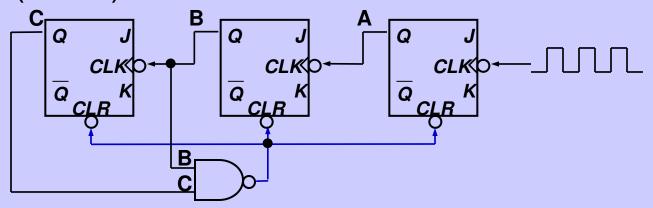

All *J*, *K* inputs are 1 (HIGH).

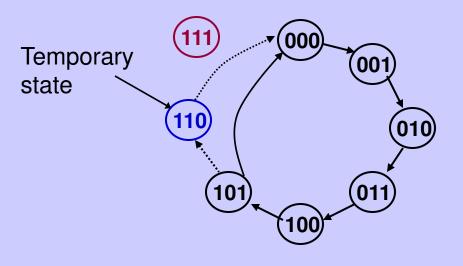

#### MOD-6 counter

produced by clearing (a MOD-8 binary counter) when count of six (110) occurs.

Example (cont'd): Counting sequence of circuit (in CBA order).

Counter is a MOD-6 counter.

- Exercise: How to construct an asynchronous MOD-5 counter? MOD-7 counter? MOD-12 counter?

- Question: The following is a MOD-? counter?

- Decade counters (or BCD counters) are counters with 10 states (modulus-10) in their sequence. They are commonly used in daily life (e.g.: utility meters, odometers, etc.).

- Design an asynchronous decade counter.

Asynchronous decade/BCD counter (cont'd).

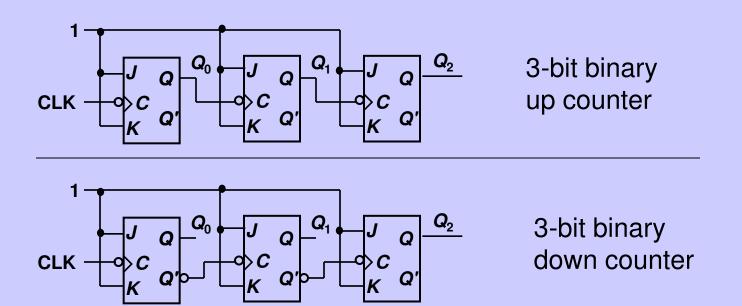

### **Asynchronous Down Counters**

- So far we are dealing with up counters. Down counters, on the other hand, count downward from a maximum value to zero, and repeat.

- Example: A 3-bit binary (MOD-2<sup>3</sup>) down counter.

#### **Asynchronous Down Counters**

Example: A 3-bit binary (MOD-8) down counter.

# **Cascading Asynchronous Counters**

- Larger asynchronous (ripple) counter can be constructed by cascading smaller ripple counters.

- Connect last-stage output of one counter to the clock input of next counter so as to achieve highermodulus operation.

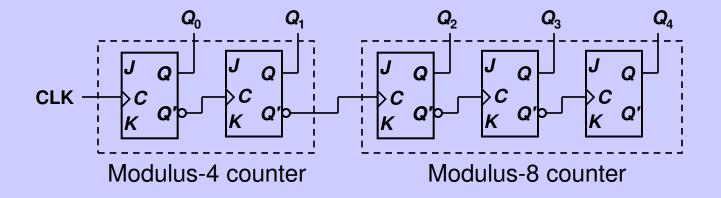

- Example: A modulus-32 ripple counter constructed from a modulus-4 counter and a modulus-8 counter.

# **Cascading Asynchronous Counters**

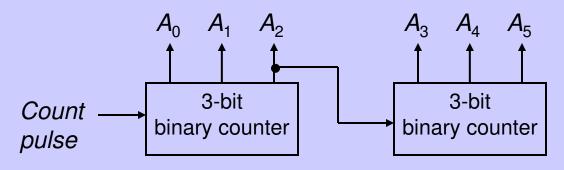

Example: A 6-bit binary counter (counts from 0 to 63) constructed from two 3-bit counters.

| $A_5$ | $A_4$ | <b>A</b> <sub>3</sub> | $A_2$ | <b>A</b> <sub>1</sub> | $A_0$ |

|-------|-------|-----------------------|-------|-----------------------|-------|

| 0     | 0     | 0                     | 0     | 0                     | 0     |

| 0     | 0     | 0                     | 0     | 0                     | 1     |

| 0     | 0     | 0                     | :     |                       | •     |

| 0     | 0     | 0                     | 1     | 1                     | 1     |

| 0     | 0     | 1                     | 0     | 0                     | 0     |

| 0     | 0     | 1                     | 0     | 0                     | 1     |

| :     | •     |                       |       | •                     | :     |

## **Cascading Asynchronous Counters**

- If counter is a not a binary counter, requires additional output.

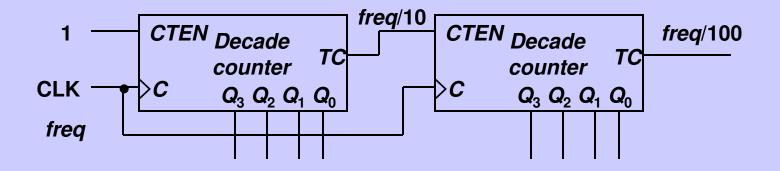

- Example: A modulus-100 counter using two decade counters.

TC = 1 when counter recycles to 0000