**Read-Only Memory**, **Programmable Devices & Sequential Programmable** Devices Lecture 5

**Dronacharya Group of Institutions**

#### Outline

- Introduction

- Random-Access Memory

- Memory Decoding

- Error Detection and Correction

- Read-Only Memory

- Programmable Devices

- Sequential Programmable Devices

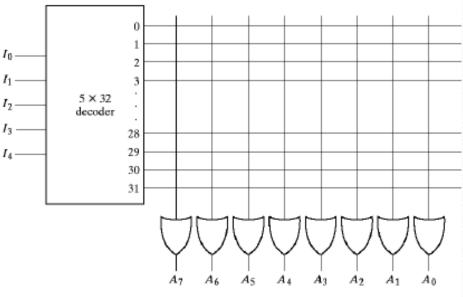

# **Read Only Memory**

- A memory device that can permanently keep binary data.

- Even when power is turned off and on again.

- For a 2k x n ROM, it consists of

- k inputs (address line) and n outputs (data).

- 2k words of n-bit each

- A k x 2k decoder (generate all minterms).

- n OR gates with 2k inputs

- Initially, all inputs of OR gates and all outputs of the decoder are fully connected.

Internal Logic of a 32 × 8 ROM

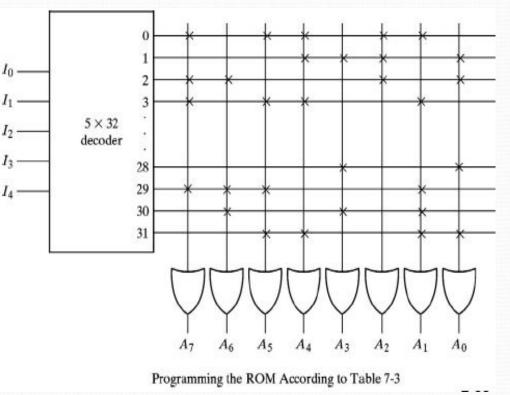

# Programming the ROM

- Each intersection (crosspoint) in the ROM is often implemented with a fuse

- Blow out unnecessary connections according to the truth table

- 1 means connected (marked as X)

- o means unconnected

- Cannot recovered after programmed

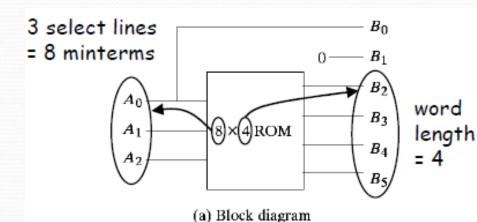

# Design Comb. Circuit with ROM

- Derive the truth table of the circuit

- Determine minimum size of ROM

- Program the ROM

|        | Outputs |        |                |                |                | Inputs         |                |                |       |                |

|--------|---------|--------|----------------|----------------|----------------|----------------|----------------|----------------|-------|----------------|

| Decima | 0       | B      | B <sub>1</sub> | B <sub>2</sub> | B <sub>3</sub> | B <sub>4</sub> | B <sub>5</sub> | A <sub>0</sub> | $A_1$ | A <sub>2</sub> |

| 0      | )       | 0      | 0              | 0              | 0              | 0              | 0              | 0              | 0     | 0              |

| 1      |         | 1      | 0              | 0              | 0              | 0              | 0              | 1              | 0     | 0              |

| 4      | )       | 0      | 0              | 1              | 0              | 0              | 0              | 0              | 1     | 0              |

| 9      |         | 1      | 0              | 0              | 1              | 0              | 0              | 1              | 1     | 0              |

| 16     | )       | 0      | 0              | 0              | 0              | 1              | 0              | 0              | 0     | 1              |

| 25     |         | 1      | 0              | 0              | 1              | 1              | 0              | 1              | 0     | 1              |

| 36     | )       | 0      | 0              | 1              | 0              | 0              | 1              | 0              | 1     | 1              |

| 49     |         | 1      | 0              | 0              | 0              | 1              | 1              | 1              | 1     | 1              |

|        | $B_2$   | B3     | $B_4$          | $B_5$          | $A_0$          | $A_2 A_1$      | A              |                |       |                |

|        | 0       | 0      | 0              | 0              | 0              | 0 0            |                |                |       |                |

|        | 0       | 0      | 0              | 0              | 1              | 0 0            |                |                |       |                |

|        | 1       | 0      | 0              | 0              | 0              |                |                |                |       |                |

|        | 0       | 1<br>0 | 0<br>1         | 0              | 1<br>0         | 01<br>10       |                |                |       |                |

|        | 0       | 1      | 1              | 0              | 1              | 1 0            |                |                |       |                |

|        | 1       | 0      | Ō              | 1              | ō              | 1 1            |                |                |       |                |

|        | 0       | 0      | 1              | 1              | 1              | 1 1            |                |                |       |                |

### Types of ROMs

- Mask programming.

- Program the ROM in the semiconductor factory.

- Economic for large quantity of the same ROM.

- Programmable ROM (PROM).

- Contain all fuses at the factory.

- Program the ROM by burning out the undesired fuses (irreversible process).

- Erasable PROM (EPROM).

- Can be restructured to the initial state under a special ultraviolet light for a given period of time.

- Electrically erasable PROM (EEPROM or E2PROM)

- Like the EPROM except being erased with electrical signals.

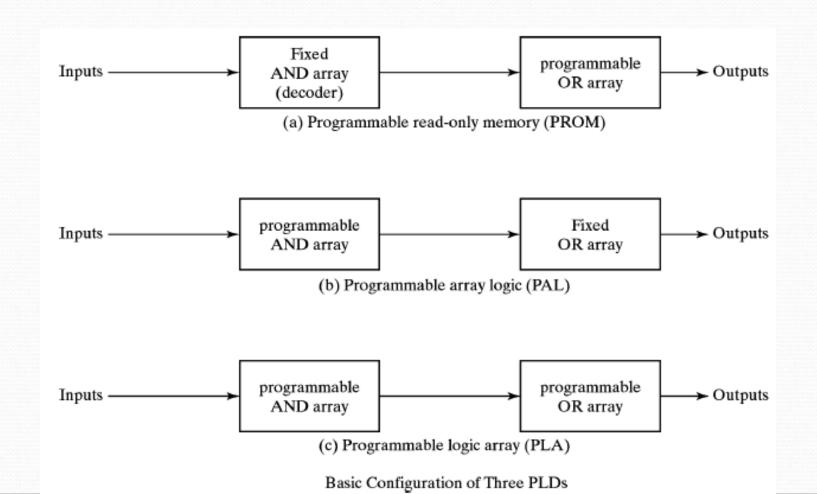

### **Programmable Logic Devices**

- ROM provides full decoding of variables.

- Waste hardware if the functions are given.

- For known combinational functions, Programmable

- Logic Devices (PLD) are often used.

- Programmable read-only memory (PROM)

- Programmable array logic (PAL)

- Programmable logic array (PLA)

- For sequential functions, we can use Sequential (simple) programmable logic device (SPLD)

- Complex programmable logic device (CPLD)

- Field programmable gate array (FPGA)

#### Outline

- Introduction

- Random-Access Memory

- Memory Decoding

- Error Detection and Correction

- Read only Memory

- Programmable Devices

- Sequential Programmable Devices

## **Configurations of Three PLDs**

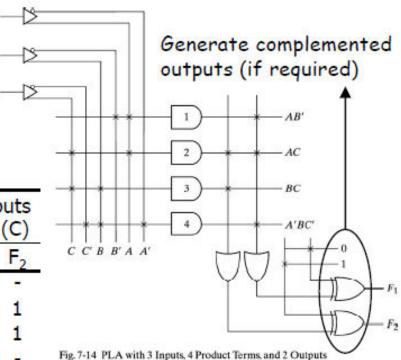

# **Programmable Logic Array**

- PLA does not provide full decoding of the variables

- Only generate the terms you need

- The decoder is replaced by an array of AND gates that can be programmed

F1 = AB' + AC + A'BC'

F2 = (AC + BC)'

|       |              | I | nput | s | Out<br>(T)     | puts<br>(C) |

|-------|--------------|---|------|---|----------------|-------------|

|       | Product Term | Α | В    | С | F <sub>1</sub> | $F_2$       |

| AB'   | 1            | 1 | 0    |   | 1              |             |

| AC    | 2            | 1 | -    | 1 | 1              | 1           |

| BC    | 3            | - | 1    | 1 | -              | 1           |

| A'BC' | 4            | 0 | 1    | 0 | 1              | 17          |

## **Implementation with PLA**

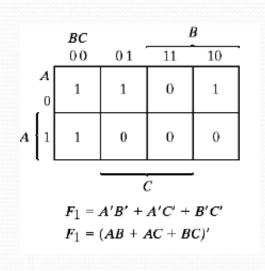

- Implement the two functions with PLA

- $F_1(A, B, C) = \Sigma (0, 1, 2, 4)$

- $F_2(A, B, C) = \Sigma (0, 5, 6, 7)$

- Goal: minimize the number of

- **Distinct product terms between** two functions

|        | ••••      | -                     |         | •      |       |       |  |  |

|--------|-----------|-----------------------|---------|--------|-------|-------|--|--|

|        |           | PLA programming table |         |        |       |       |  |  |

|        |           |                       |         | Out    | puts  |       |  |  |

|        |           | Produc                |         | puts   | (C)   | (T)   |  |  |

|        |           | term                  | A       | BC     | $F_1$ | $F_2$ |  |  |

| A      | AB        |                       | 1       | 1 -    | 1     | 1     |  |  |

| AC     |           | 2                     | 1       | - 1    | 1     | 1     |  |  |

| BC     |           | 3                     | _       | 1 1    | 1     | -     |  |  |

| A'B'C' |           | 4                     | 0       | 0 0    | _     | 1     |  |  |

|        | BC        |                       | I       |        |       |       |  |  |

|        | 0.0       | 01                    | 11      | 10     | -     |       |  |  |

| A<br>0 | 1         | 0                     | 0       | 0      |       |       |  |  |

| A [1   | 0         | 1                     | 1       | 1      |       |       |  |  |

|        |           | Ċ                     | 2       |        |       |       |  |  |

|        | $F_2 = 1$ | AB + AC               | C + A'I | B'C'   |       |       |  |  |

|        | $F_2 = ($ | (A'C + A)             | A'B + A | AB'C') | ,     |       |  |  |

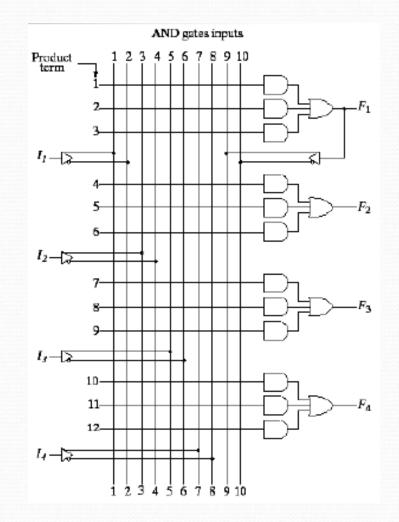

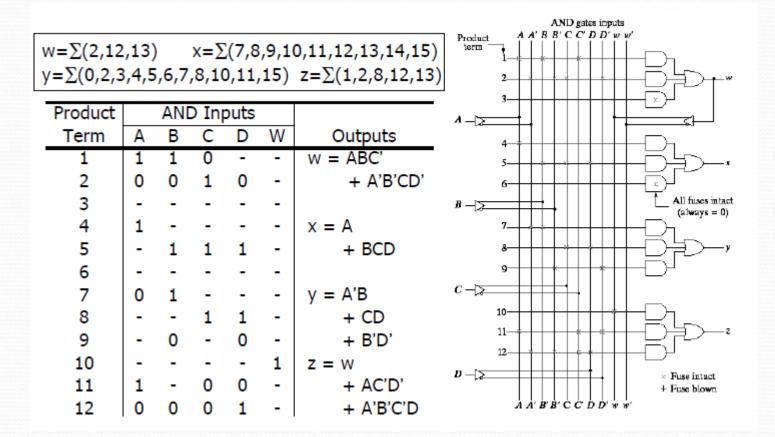

### Programmable Array Logic

PAL has a fixed OR array and a programmable AND array.

Easier to program but not as flexible as PLA.

Each input has a buffer inverter Gate.

One of the outputs is fed back as two inputs of the AND gates.

Unlike PLA, a product term cannot be shared among gates

Each function can be simplified by itself without common terms.

#### Implementation with PAL

#### Outline

- Introduction

- Random-Access Memory

- Memory Decoding

- Error Detection and Correction

- Read only Memory

- Programmable Devices

- Sequential Programmable Devices

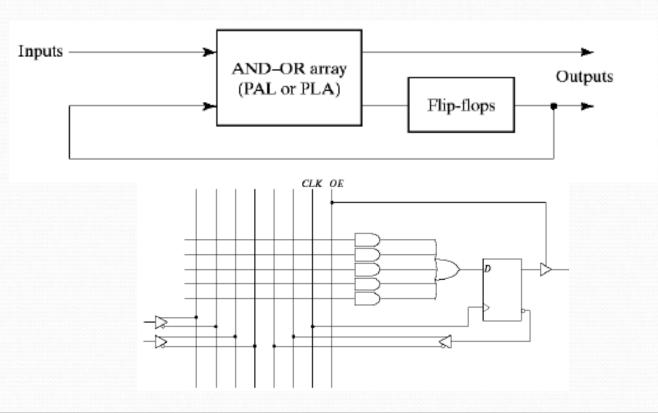

# Sequential PLD

The most simple sequential PLD = PLA (PAL) + Flip-Flops.

The mostly used configuration for SPLD is constructed with 8 to 10 macrocells as shown right.

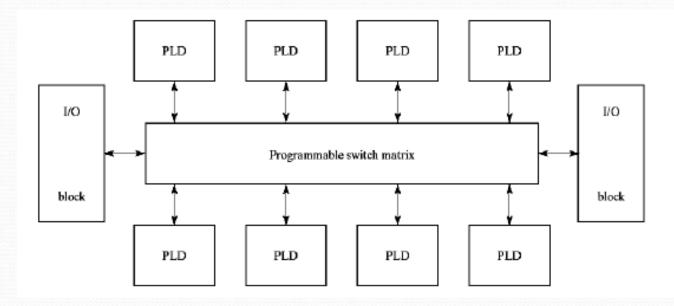

#### **Complex PLD**

- Complex digital systems often require the connection of several devices to produce the complex specification.

- More economical to use a complex PLD (CPLD).

- CPLD is a collection of individual PLDs on a single IC with programmable interconnection structure.

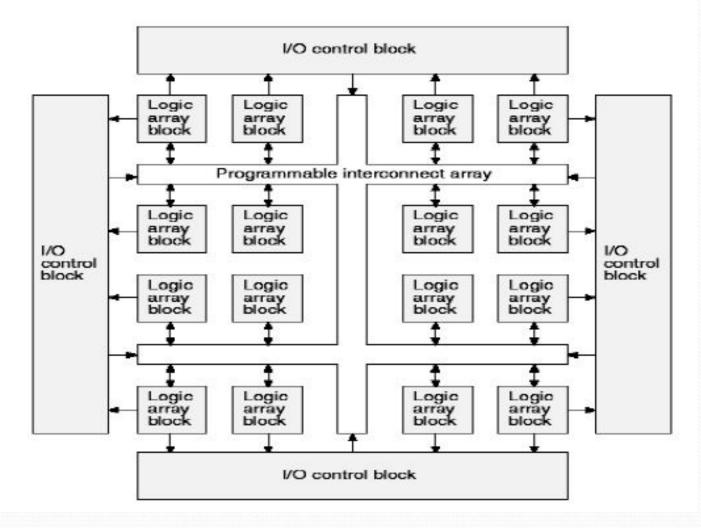

### Field Programmable Gate Array

- Gate array: a VLSI circuit with some pre-fabricated gates repeated thousands of times.

- Designers have to provide the desired interconnection patterns to the manufacturer (factory).

- A field programmable gate array (FPGA) is a VLSI circuit that can be programmed in the user's location.

- Easier to use and modify

- Getting popular for fast and reusable prototyping

- There are various implementations for FPGA

# FPGA Structure (Altera)