BASIC INTERFACING CONCEPTS: INTERFACING OUTPUT DISPLAYS & INPUT DEVICES, MEMORY MAPPED I/O, FLOW CHART SYMBOLS LECTURE 1

Dronacharya Group of institutions

# 8085 interfacing with I/O Devices

Microprocessor need to Identify I/O devices with binary number.IO devices can be interfaced:

•Memory-Mapped I/O (using addresses from memory space): Device is identified by 16-bit address (Space ranges from 0000H -FFFFH.

•Standard I/O mapped or isolated I/O mapping /Peripheral Mapped I/O has separate numbering scheme for I/O devices. Instructions IN/OUT are used for data transfer. Device is identified by 8-bit address (Space ranges from 00H –FFH).

### Memory Mapping Vs Peripheral I/O

| Memory Mapping of I/O device                                                                                                                                                                                                    | I/O Mapping of I/O device                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                 | <ol> <li>8-bit addresses are provided for I/O devices.</li> <li>The devices are accessed by I/O read or I/O<br/>write cycle. During these cycles the 8-bit<br/>address is available on both low order address<br/>lines and high order address lines.</li> </ol> |

| 3. The I/O ports or peripherals can be treated<br>like memory locations and so all instructions<br>related to memory can be used for data<br>transfer between I/O device and the processor.                                     | processor.                                                                                                                                                                                                                                                       |

| <ol> <li>In memory mapped ports the data can be<br/>moved from any register to ports and vice-<br/>versa.</li> </ol>                                                                                                            | <ol> <li>In I/O mapped ports the data transfer can take<br/>place only between the accumulator and ports.</li> </ol>                                                                                                                                             |

| 5. When memory mapping is used for I/O<br>devices, the full memory address space cannot<br>be used for addressing memory. Hence<br>memory mapping is useful only for small<br>systems, where the memory requirement is<br>less. | <ol> <li>When I/O mapping is used for I/O devices<br/>then the full memory address space can be<br/>used for addressing memory. Hence it is<br/>suitable for systems which requires large<br/>memory capacity.</li> </ol>                                        |

| <ul> <li>6. In memory mapped I/O devices, a large number of I/O ports can be interfaced.</li> <li>7. For accessing the memory mapped devices,</li> </ul>                                                                        | <ul> <li>6. In I/O mapping only 256 ports<br/>(2<sup>8</sup> = 256) can be interfaced.</li> <li>7. For accessing the I/O mapped devices, the</li> </ul>                                                                                                          |

| the processor executes memory read or write cycle. During this cycle IO/ $\overline{M}$ is asserted low $(IO/\overline{M} = 0)$ .                                                                                               | processor executes I/O read or write cycle.                                                                                                                                                                                                                      |

# **Peripheral I/O Instructions**

Instruction IN (code DB) inputs data from an input device into accumulator.

| Opcode            | Operand                   | Description                              |

|-------------------|---------------------------|------------------------------------------|

| IN                | 8-bit Port address        | 2-byte instruction with hexadecimal      |

|                   |                           | instruction DB and second byte is        |

| port              |                           | and the set in set in second description |

|                   |                           | number of input device.                  |

|                   |                           |                                          |

| Memory            | Machine Code              | Mnemonics                                |

| Memory<br>Address | Machine Code              | Mnemonics                                |

| U                 | <b>Machine Code</b><br>DB | <b>Mnemonics</b><br>IN 84                |

| Address           |                           |                                          |

Instruction OUT (code D3) sends the content of the accumulator to output device such as LED display.

| Opcode  | Operand             | Description                            |

|---------|---------------------|----------------------------------------|

| OUT     | 8-bit Port address  | 2-byte instruction with hexadecimal    |

|         |                     | instruction D3 and Second byte is port |

|         |                     | number of output device.               |

| Memory  | <b>Machine Code</b> | Mnemonics                              |

| Address |                     |                                        |

| 2050    | D3                  | OUT 01                                 |

| 2051    | 01                  |                                        |

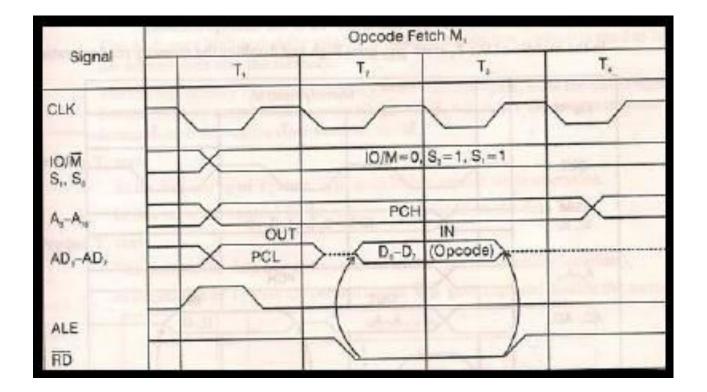

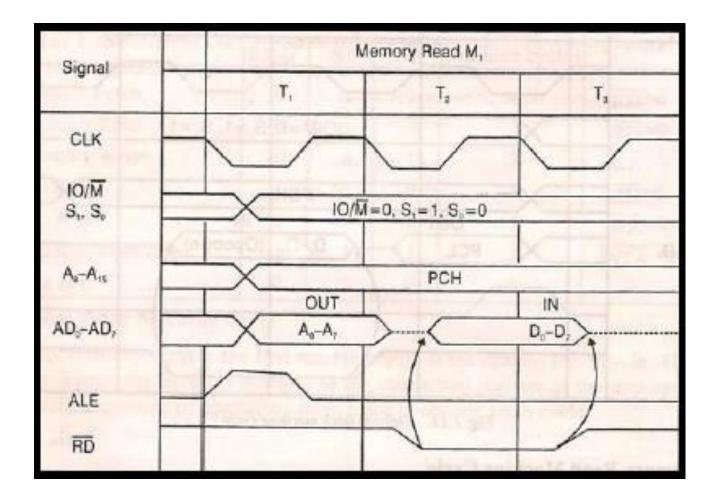

## MACHINE CYCLE STATUS AND CONTROL SIGNALS

| Machine Cycle    | Status |    |    | No. of         | Control                    |

|------------------|--------|----|----|----------------|----------------------------|

|                  | IO/M   | S1 | SO | Machine cycles | control                    |

| Opcode Fetch     | 0      | 1  | 1  | 4              | RD=0                       |

| Memory Read      | 0      | 1  | 0  | 3              | $\overline{RD} = 0$        |

| Memory Write     | 0      | 0  | 1  | 3              | $\overline{WR} = 0$        |

| I/O Read         | 1      | 1  | 0  | 3              | $\overline{\text{RD}} = 0$ |

| I/O Write        | 1      | 0  | 1  | 3              | WR =0                      |

| INTR Acknowledge | 1      | 1  | 1  | 3              | INTA =0                    |

| Bus Idle         | 0      | 0  | 0  | 3              | I STOLL STO                |

#### **MEMORY READ MACHINE CYCLE**

### **I/O READ MACHINE CYCLE**

#### **OUT Instruction**

• In First Machine cycle M1(Opcode Fetch), microprocessor places the 16-bit memory address from the program counter (PC) on the address bus. At T1 20H is placed on A15-A8 and 50H is placed on AD7-AD0. ALE goes high, IO/M' goes low indicates memory related operations.

• ALE indicates the availability of the address on AD7-AD0. At T2 microprocessor sends RD' control signal which is combined with IO/M' to generate MEMR' signal and processor fetches the instruction code D3 using data bus.

#### **OUT Instruction**

- M2 (memory Read), 8085 places next address 2051H on address bus and get device address 01H.

- M3 (I/O write), 8085 place device address 01H on low and high address bus both.IO/M' goes high to indicate I/O operation. At T2 AC contents are placed on data bus followed by control signal WR'. If we connect data bus to latch we can catch the information and display on LEDs and Printer. By ANDing IO/M' and WR' signals IOW' signal enable output device.

- Information necessary for interfacing output device is available during T2 and T3 of the M3 cycle.

### **IN Instruction**

• In First Machine cycle M1 (Opcode Fetch), microprocessor places the 16-bit memory address from the program counter (PC) on the address bus. At T1 20H is placed on A15-A8 and 65H is placed on AD7-AD0. ALE goes high, IO/M' goes low indicates memory related operations. ALE indicates the availability of the address on AD7-AD0. At T2 microprocessor sends RD' control signal which is combined with IO/M' to generate MEMR' signal and processor fetches the instruction code DB using data bus.

• M2 (Memory Read), 8085 places next address 2066H on address bus and get device address 84H.

• M3 (Memory Read), 8085 place device address 84H on low and high address bus both and asserts RD' signal. IO/M' goes high to indicate IO operation. At T2 data from input port are paced on data bus and transferred to AC. By ANDing IO/M' and WR' signals IOR' signal to enable input port.

#### **Data Transfer**

For data transfer from input device to processor the following operations are performed.

- •The input device will load the data to the port. •When the port receives a data, it sends message

- •When the port receives a data, it sends message to the processor to read the data.

- •The processor will read the data from the port.

- •After a data have been read by the processor the input device will load the next data into the port.

#### **Data Transfer**

For data transfer from processor to output device the following operations are performed.

- •The processor will load the data to the port.

- •The port will send a message to the output device to read the data.

- •The output device will read the data from the port.

- •After the data have been read by the output device the processor can load the next data to the port.