# 8086 MICROPROCESSOR REGISTER ORGANIZATION LECTURE 7

# 8086 Programmer's Model

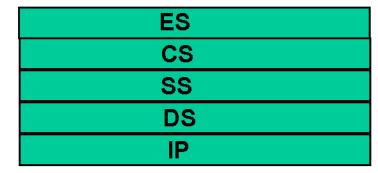

BIU registers (20 bit adder)

Extra Segment

Code Segment

Stack Segment

Data Segment

Instruction Pointer

BX CX DX

EU registers 16 bit arithmetic

| AH  | AL    |

|-----|-------|

| ВН  | BL    |

| CH  | CL    |

| DH  | DL    |

| S   | SP SP |

| В   | 3P    |

| S   | il e  |

|     | )I    |

| FLA | GS    |

|     | •     |

Accumulator

Base Register

Count Register

Data Register

Stack Pointer

Base Pointer

Source Index Register

Destination Index Register

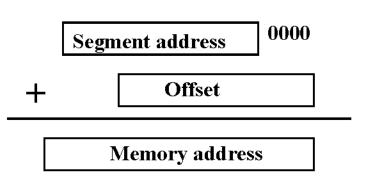

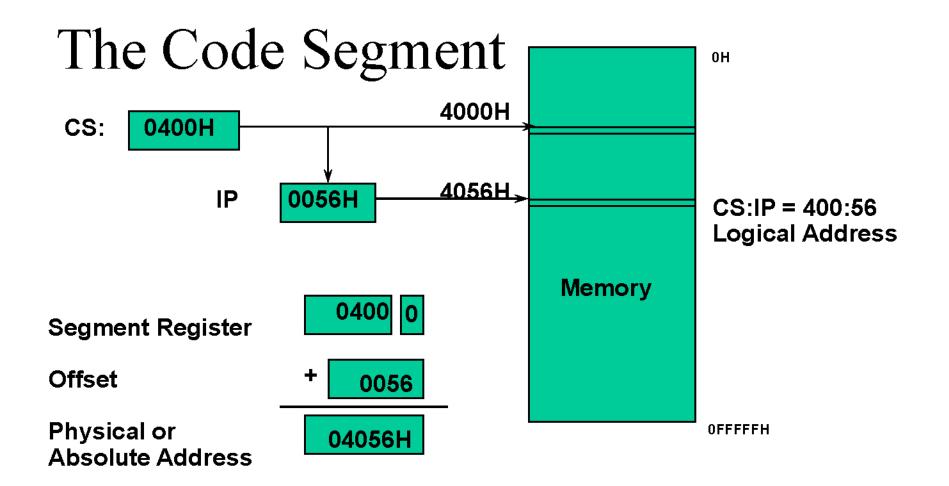

### **Memory Address Calculation**

- ☐ Segment addresses must be stored in segment registers

- ☐ Offset is derived from the combination of pointer registers, the Instruction Pointer (IP), and immediate values

□ Examples

| CS                  | 3 | 4 | 8 | A | 0 |

|---------------------|---|---|---|---|---|

| IP +                |   | 4 | 2 | 1 | 4 |

| Instruction address | 3 | 8 | A | В | 4 |

| SS            | 5 | 0 | 0 | 0 | 0 |

|---------------|---|---|---|---|---|

| SP +          |   | F | F | E | 0 |

| Stack address | 5 | F | F | E | 0 |

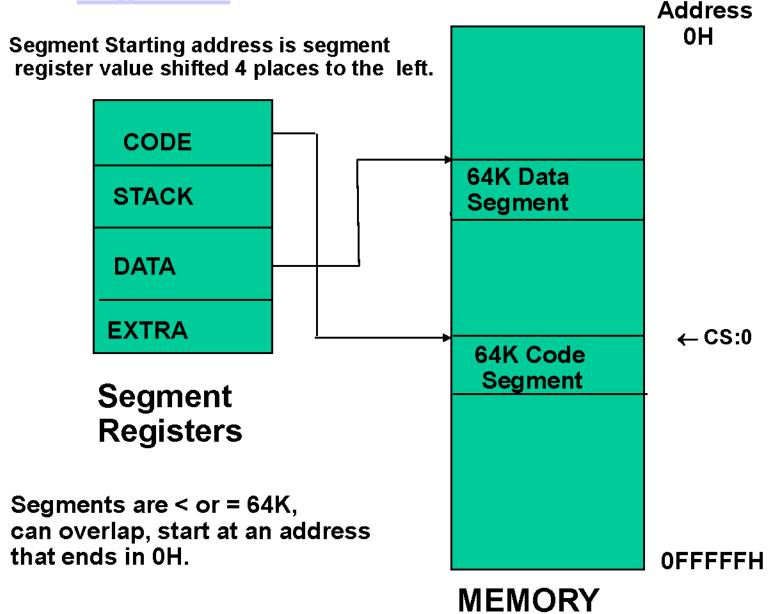

#### **Segments**

# 8086 Memory Terminology

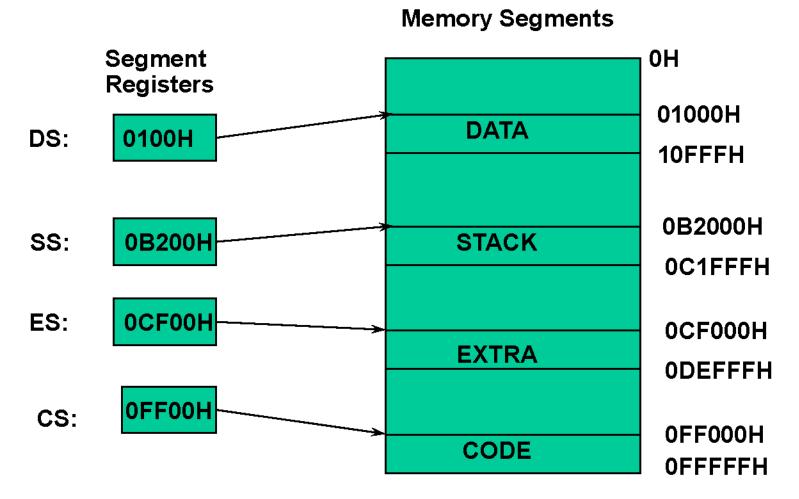

Segments are < or = 64K and can overlap.

Note that the Code segment is < 64K since 0FFFFH is the highest address.

The offset is the distance in bytes from the start of the segment. The offset is given by the IP for the Code Segment. Instructions are always fetched with using the CS register.

The <u>physical address</u> is also called the <u>absolute address</u>.

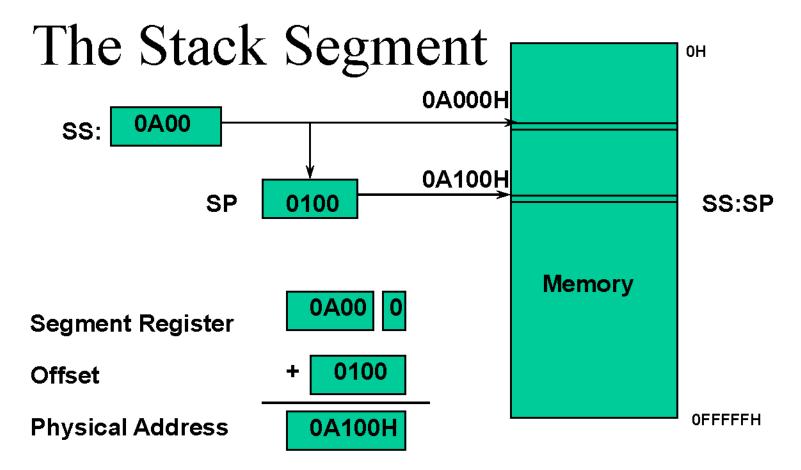

The offset is given by the SP register.

The stack is always referenced with respect to the stack segment register.

The stack grows toward decreasing memory locations.

The SP points to the last or top item on the stack.

PUSH - pre-decrement the SP POP - post-increment the SP

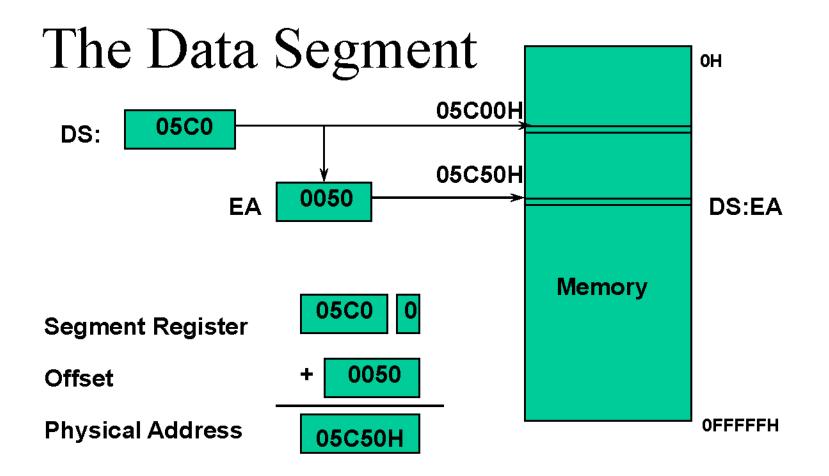

Data is usually fetched with respect to the DS register. The effective address (EA) is the offset. The EA depends on the addressing mode.

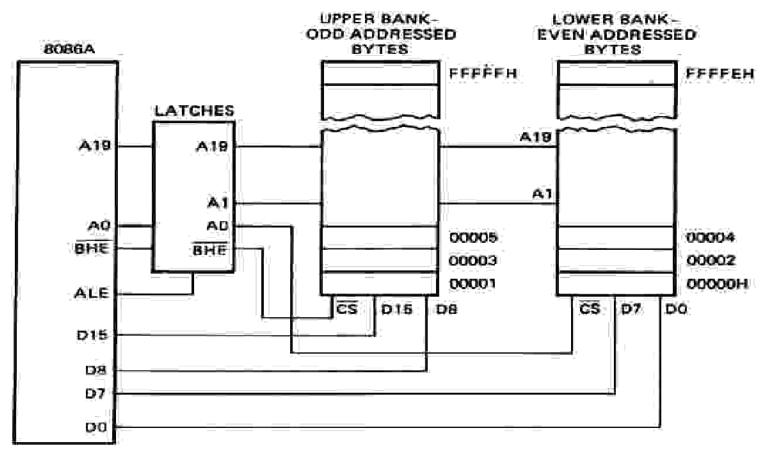

# 8086 memory Organization

(a)

| ADDRESS | DATA<br>TYPE | BHE | Ao    | BUS<br>CYCLES | DATA<br>LINES USED |

|---------|--------------|-----|-------|---------------|--------------------|

| 0000    | BYTE         | 7   | O     | ONE           | D0-D7              |

| 0000    | WORD         | 0   | 0     | ONE           | DO-D15             |

| 0001    | BYTE         | O   | 1     | ONE           | DE D15             |

| 0001    | WORD         | 0   | ing i | FIRST         | D0-D8 €            |

|         |              | 3   | 0     | SECOND        | DA-D15 🕳           |

Even addresses are on the low half of the data bus (D0-D7).

Odd addresses are on the upper half of the data bus (D8-D15).

A0 = 0 when data is on the low half of the data bus.

BHE' = 0 when data is on the upper half of the data bus.