## Unit 3 Combinational MOS Logic Circuits

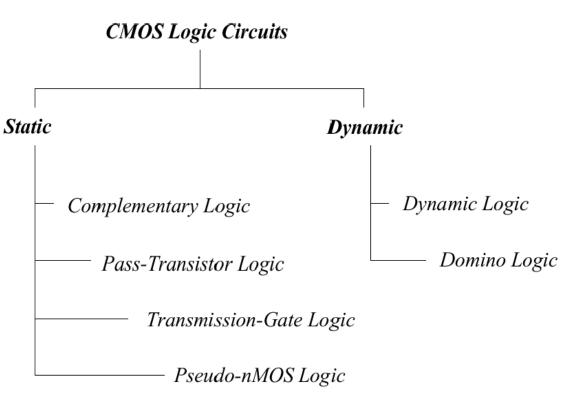

# **CMOS Logic Structures**

- Static logic circuits hold their output values indefinitely

- Dynamic logic circuits store the output in a capacitor, so it decays with time unless it is refreshed.

- We will look at a few of these structures

Different structures of CMOS logic circuits.

• Transistors can be used as switches

$$g = 0$$

$$g = 0$$

$$g = 1$$

$$1 \longrightarrow degraded 1$$

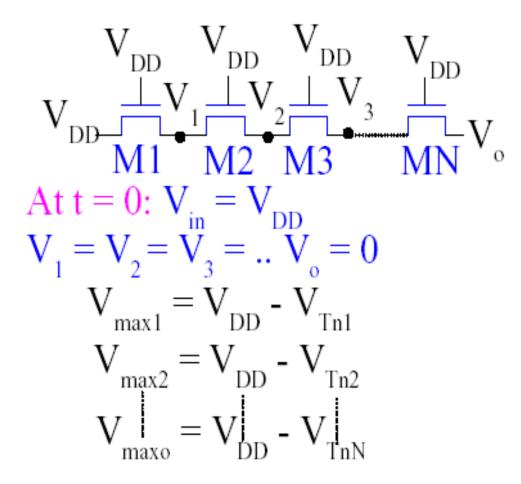

- Pass-transistor circuits are formed by dropping the PMOS transistors and using only NMOS pass transistors

- In this case, CMOS inverters (or other means) must be used periodically to recover the full  $V_{DD}$  level since the NMOS pass transistors will provide a  $V_{OH}$  of  $V_{DD} V_{Tn}$  in some cases

- The pass transistor circuit requires complementary inputs and generates complementary outputs to pass on to the next stage

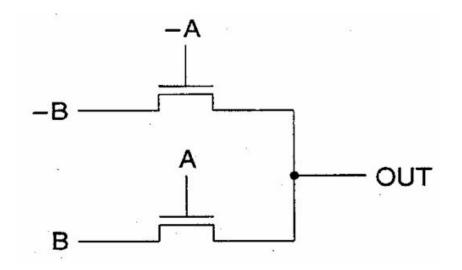

- This figure shows a simple XNOR implementation using pass transistors:

- If A is high, B is passed through the gate to the output

- If A is low, -B is passed through the gate to the output

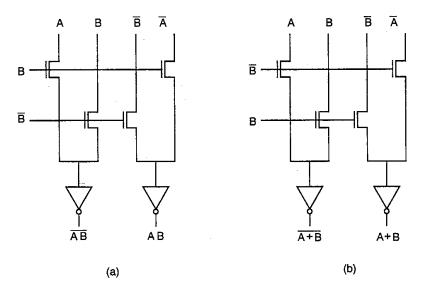

- At right,

- (a) is a 2-input NAND pass transistor circuit

- (b) is a 2-input NOR pass transistor circuit

- Each circuit requires 8 transistors, double that required using conventional CMOS realizations

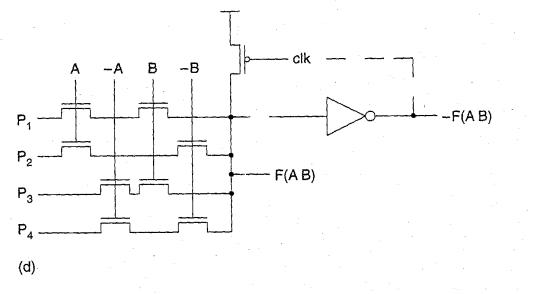

- Pass-transistor logic gate can implement Boolean functions NOR, XOR, NAND, AND, and OR depending upon the P1-P4 inputs, as shown below.

- P1,P2,P3,P4 = 0,0,0,1 gives F(A,B) = NOR

- P1,P2,P3,P4 = 0,1,1,0 gives F(A,B) = XOR

- P1,P2,P3,P4 = 0,1,1,1 gives F(A,B) = NAND

- P1,P2,P3,P4 = 1,0,0,0 gives F(A,B) = AND

- P1,P2,P3,P4 = 1,1,1,0 gives F(A,B) = OR

Circuit can be operated with clocked P pull-up device or inverterbased latch

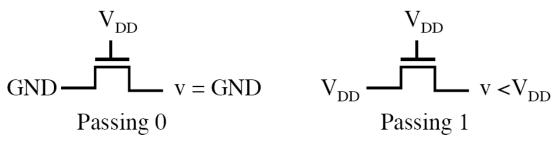

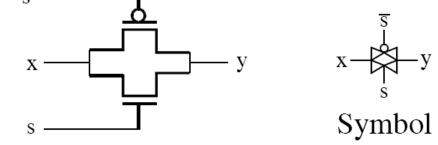

• N-Channel MOS Transistors pass a 0 better than a 1

• P-Channel MOS Transistors pass a 1 better than a 0

• This is the reason that N-Channel transistors are used in the pull-down network and P-Channel in the pull-up network of a CMOS gate. Otherwise the noise margin would be significantly reduced.

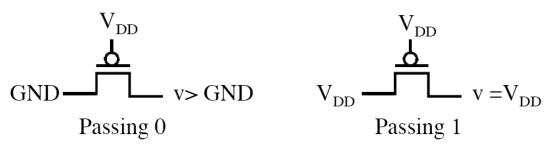

A transmission gate is a essentially a switch that connects two points. In order to pass 0's and 1's equally well, a pair of transistors (one N-Channel and one P-Channel) are used as shown below:

Circuit

- When s = 1 the two transistors conduct and connect x and y

- The top transistor passes x when it is 1 and the bottom transistor passes x when it is 0

- When s = 0 the two transistor are cut off disconnecting x and y

- Pass transistors produce degraded outputs

- Transmission gates pass both 0 and 1 well

|                            |                          | Input           | Output                |

|----------------------------|--------------------------|-----------------|-----------------------|

| g                          | g = 0, gb = 1<br>a⊸∽‴∽ b | g = 1, g<br>0⊸⊶ | gb = 0<br>∞– strong 0 |

| a - <u></u> ⊦ b<br>∫<br>gb | g = 1, gb = 0<br>a⊸⊶ b   | g = 1, g<br>1⊸→ | gb = 0<br>∞– strong 1 |

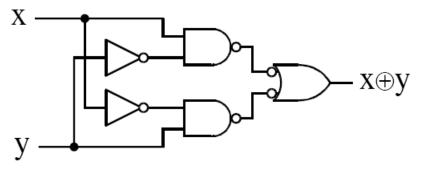

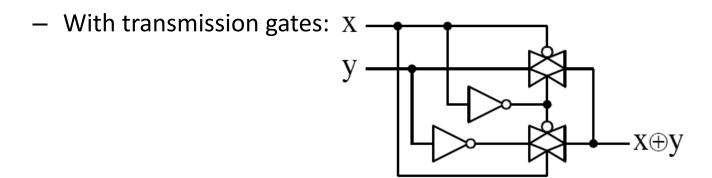

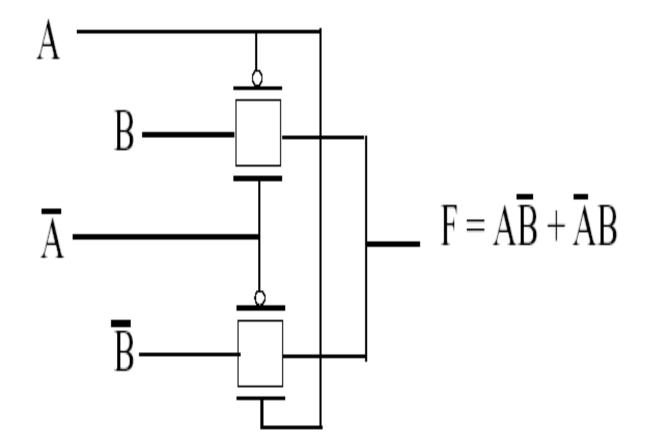

- Implementing XOR gates

- With NAND gates and inverters:

• Why would one of these circuits be preferable to the other?

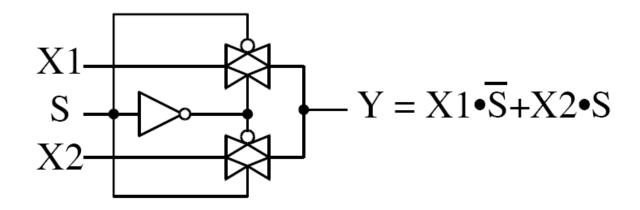

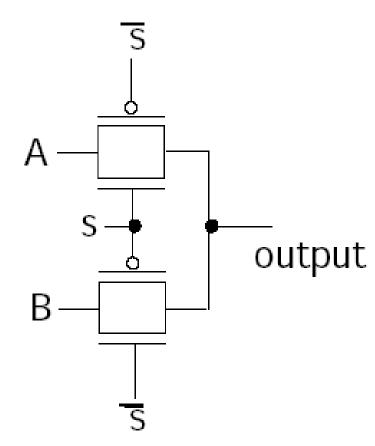

• Implementing a multiplexer with transmission gates:

- When S = 0, input X1 is connected to the output Y

- When S = 1, input X2 is connected to the output Y

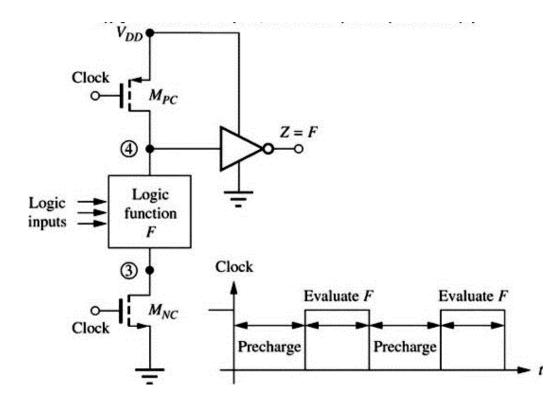

# Dynamic Domino CMOS Logic

- One technique to help decrease power in MOS logic circuits is dynamic logic

- Dynamic logic uses different precharge and evaluation phases that are controlled by a system clock to eliminate the dc current path in single channel logic circuits

- Early MOS logic required multiphase clocks to accomplish this, but CMOS logic can be operated dynamically with a single clock

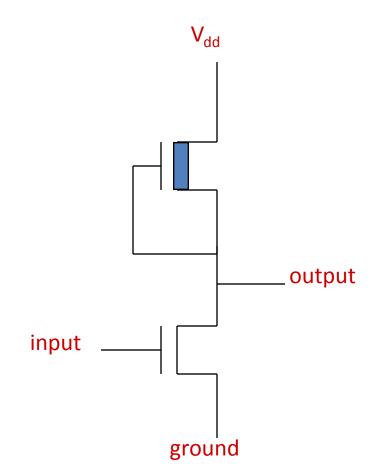

# Static NMOS

- Totem-Pole Output

- as we have seen previously

- Does not need to be refreshed

- Which is why it is called static

- PMOS Acts as Constant Current Source for Active Pull-Up

- Faster rise-times as compared to non-CMOS implementations

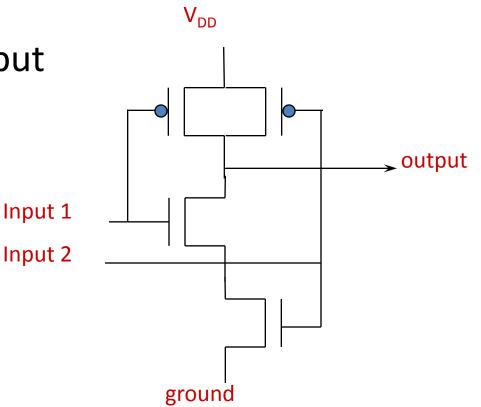

# Static CMOS

- Complementary MOS

- Example of a 2-input NAND gate

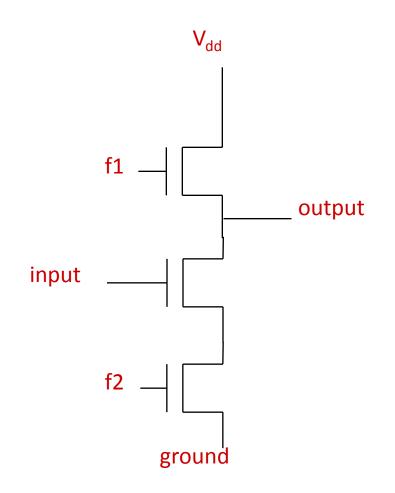

# Dynamic NMOS

- Output is "1" unless discharged

- f<sub>1</sub> Charges Output

- f<sub>2</sub> Conditionally Discharges Output

# Dynamic Domino CMOS Logic

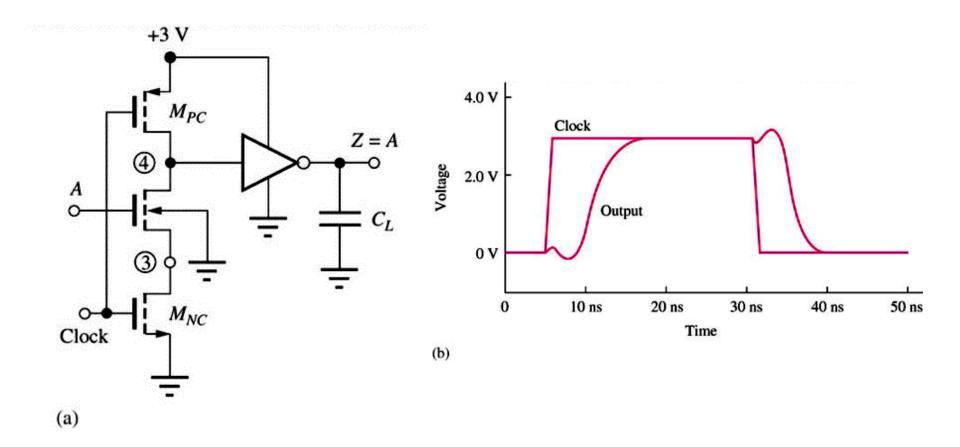

• The figure demonstrates the basic concept of domino CMOS logic operation

## Simple Dynamic Domino Logic Circuit

# Dynamic Domino CMOS Logic

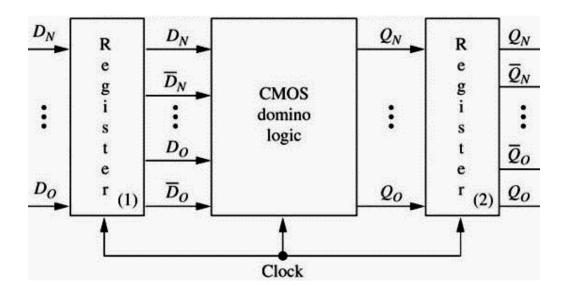

- Domino CMOS circuits only produce true logic outputs

- This can be overcome by using registers that have both true and complemented output to complete the function shown by the following circuit:

# Pass Transistor Logic

## **Pass Transistor Logic Circuits**

**nMOS** Pass transistor – transmission properties

Transmission Gates

#### □ Transmission Gate Applications

- Mux

- □ XOR

- D Latch

- D Flip Flop

- Clock Skew management

- Pass Transistor Logic Families

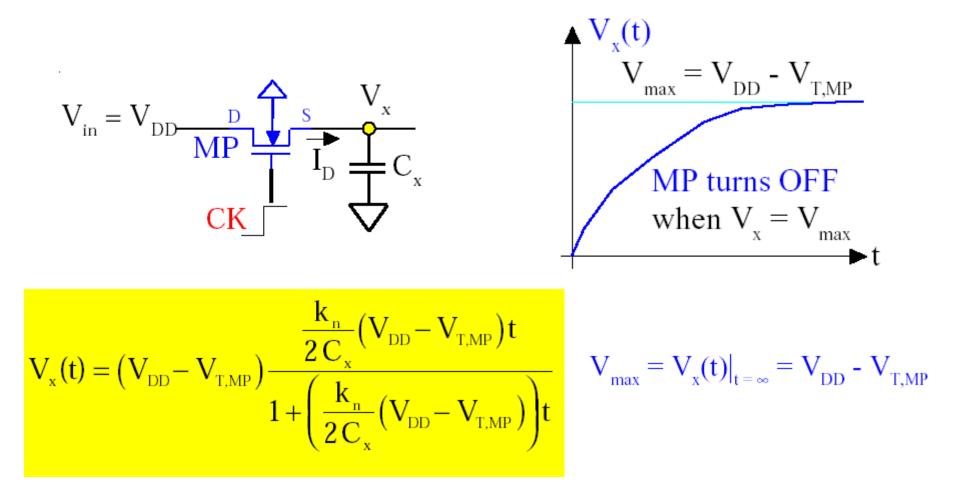

## nMOS Pass Transistor – Logic '1' Transfer

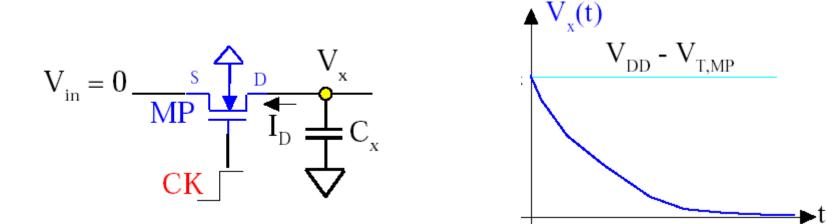

## nMOS Pass Transistor – Logic '0' Transfer

#### Pass Transistor Logic

- 1. Very efficient in use of transistors.

- 2. Potentially very efficient layouts result.

- 3. Pass transistors can usually be minimum size devices.

- 4. Usually more internal node capacitance than with conventional CMOS gates.

- 5. Propogation delays can become large in long series strings of pass transistors.

6. Use of CMOS transmission gates circumvents the  $V_{Tn}$  voltage drop of nMOS pass-transistors. It also doubles the area and interconnects.

- 7. Static power dissipation is uneffected.

- 8. Dynamic power dissipation may be decreased.

## **PASS TRANSISTORS IN SERIES**

## PASS TRANSISTOR LOGIC CIRCUITS

nMOS Pass transistor – transmission properties

#### **Transmission Gates**

□ Transmission Gate Applications

- Mux

- XOR

- D Latch

- D Flip Flop

- Clock Skew management

- Pass Transistor Logic Families

#### **TRANSMISSION GATES**

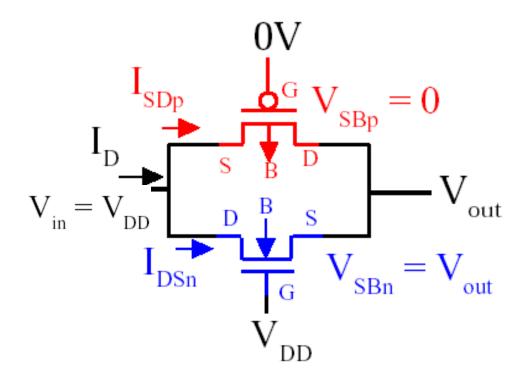

NMOS pass transistor passes a *strong* 0 and a *weak* 1.

PMOS pass transistor passes a *strong* 1 and a *weak* 0.

Combine the two to make a CMOS pass gate which will pass a *strong* 0 and a *strong* 1.

#### **TRANSMISSION GATE**

## **PROBLEMS WITH TRANSMISSION GATES**

□ No isolation between the input and output.

Output progressively deteriorates as it passes through various stages.

However designs get simplified.

## PASS TRANSISTOR LOGIC CIRCUITS

- □ nMOS Pass transistor transmission properties

- Transmission Gates

#### □ Transmission Gate Applications

- Mux

- □ XOR

- D Latch

- D Flip Flop

- Clock Skew management

- Pass Transistor Logic Families

#### **Multiplexor**

| output = $A.s + B.\overline{s}$ |   |   |   |                    |        |  |

|---------------------------------|---|---|---|--------------------|--------|--|

|                                 | А | В | s | $\cdot \mathbf{S}$ | output |  |

|                                 | X | 0 | 0 | 1                  | 0 (B)  |  |

|                                 | х | 1 | 0 | 1                  | 1 (B)  |  |

|                                 | 0 | x | 1 | 0                  | 0 (A)  |  |

|                                 | 1 | х | 1 | 0                  | 1 (A)  |  |

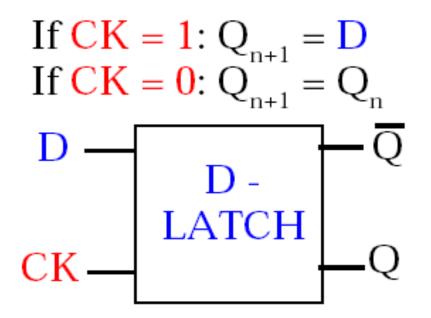

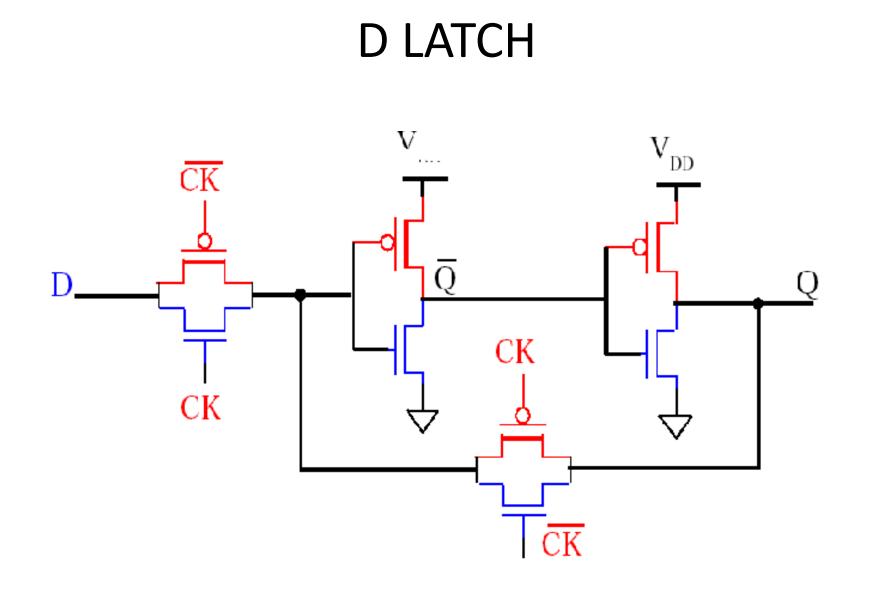

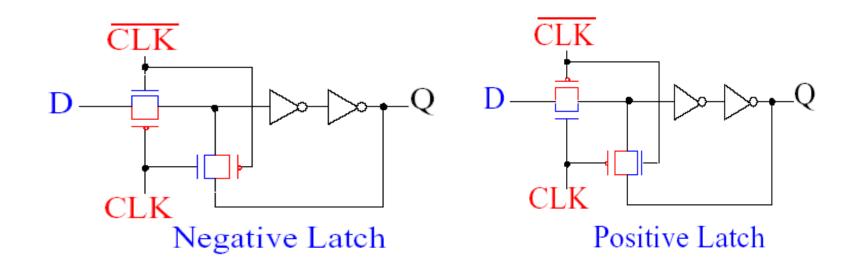

#### D – Latch

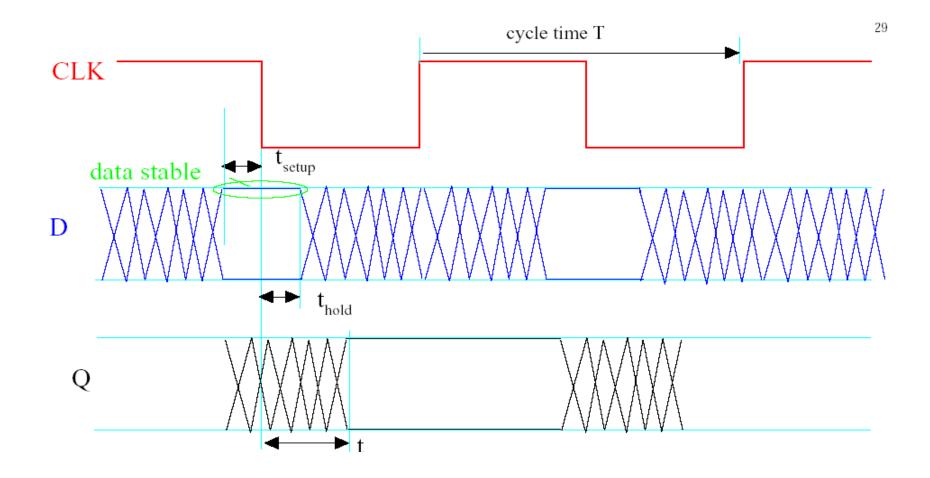

#### TIMING ISSUES

#### D - LATCH

#### D LATCH – ALTERNATE CIRCUIT TOPOLOGY

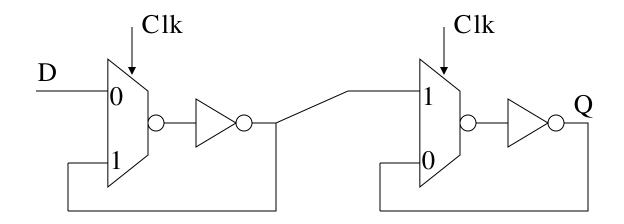

#### **Static Flip Flop**

Transparent whenTransparent whenClk=0Clk=1

At Clk=  $0 \rightarrow 1$ , Q = D. Else Q is held.

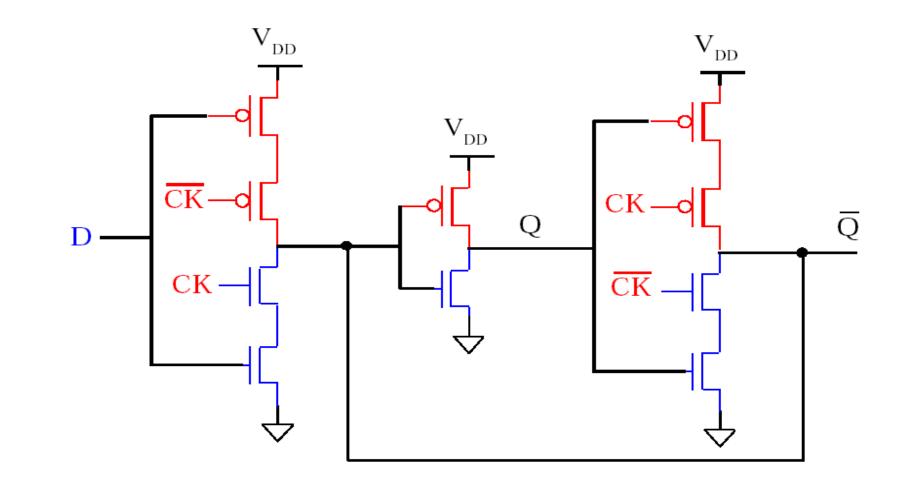

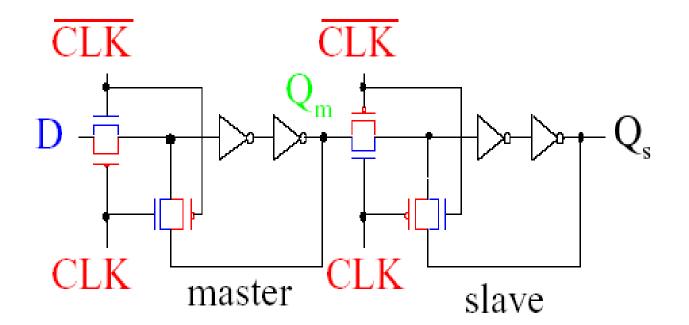

# D Flip Flop – Circuit Diagram

#### **D** Flip Flop - Operation

1. CLK = 0: master  $Q_m$  tracks current D; slave  $Q_s$  = previous D sample ( $Q_s$  is transparent to variations in D).

2.  $CLK = 0 \rightarrow 1$ : master stores  $Q_m = D$  (new D sample).

3. CLK = 1: master passes  $Q_m = D$  to slave output  $Q_s(Q_m \text{ and } Q_s \text{ are transparent to} variations in D).$

4. CLK = 1 -> 0: slave locks in new D, and master  $Q_m$  begins tracking D.

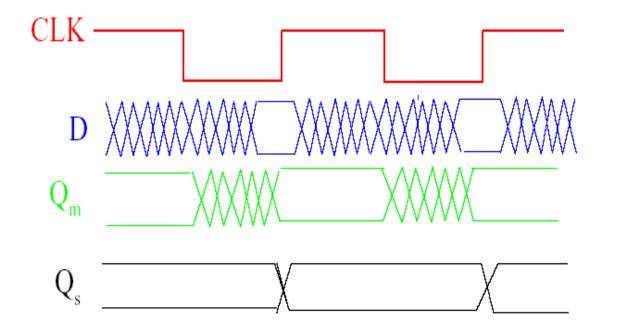

#### D Flip Flop - Waveforms

Q<sub>s</sub> stored when CLK high and available when CLK high and low

#### Pass Transistor Logic Circuits

- nMOS Pass transistor transmission properties

- Transmission Gates

#### □ Transmission Gate Applications

- Mux

- XOR

- D Latch

- D Flip Flop

- Clock Skew management

- Pass Transistor Logic Families

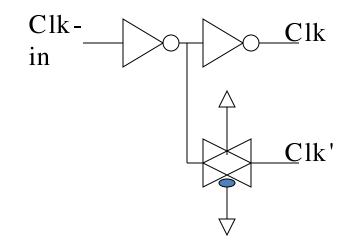

#### Handling Clock Skew

## Pass Transistor Logic Families

- Complementary Pass Transistor Logic Family

- Dual Pass Transistor Logic Family

- □ Swing Restored Pass Transistor Logic Family