# Unit 5 LECTURE 3

## 8254 Programmable Interval Timer

- It generates accurate time delays and can be used as real time clock, and event counter, a digital one shot, a square wave generator and complex waveform generator.

- 3 identical 16 bit counters that can operate independently in any 6 modes.

- 24 Pin DIP.

- 16 bit count is loaded in its register and on command begins to decrement the count until it reaches 0.

- At end of count, it generates a pulse that can be used to interrupt MPU. Counter can count either in BCD or binary.

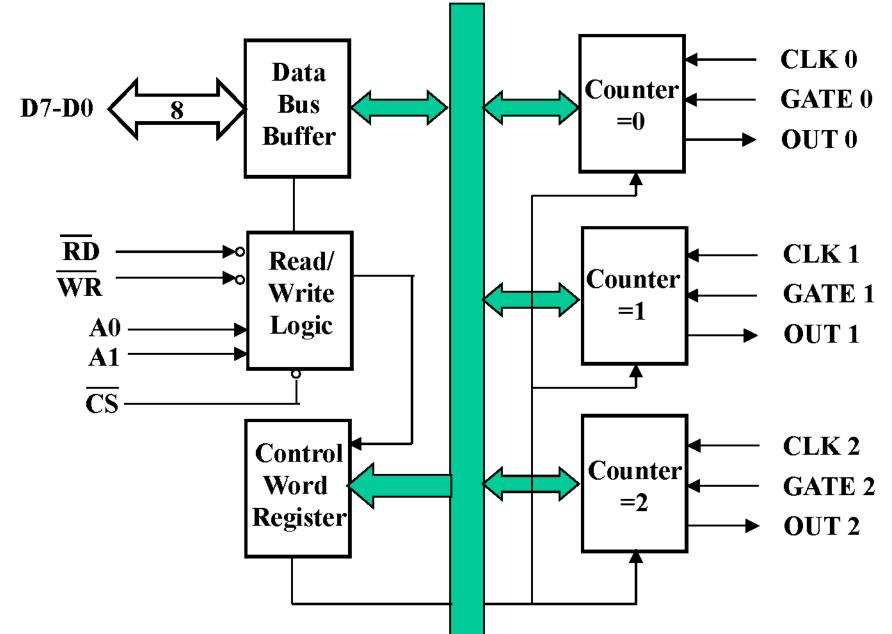

### 8254 Internal Architecture

# THE CONTROL WORD REGISTER AND COUNTERS ARE SELECTED ACCORDING TO THE SIGNALS ON LINE A0 and A1 AS SHOWN BELOW

#### A1 A0 Selection

- 0 0 Counter 0

- 0 1 Counter 1

- **1 0 Counter 2**

- 1 1 Control Register

### 8254 Control Word Format

|                                      |                                              | SC1 SC0 RV        | V1     F | 1    RW0    M2    M1    M0    BCD |                                          |  |

|--------------------------------------|----------------------------------------------|-------------------|----------|-----------------------------------|------------------------------------------|--|

|                                      |                                              |                   | RW1      | RW0                               |                                          |  |

| SC1                                  | SC0                                          |                   |          |                                   |                                          |  |

|                                      |                                              |                   | 0        | $\parallel _{0} - \parallel$      | Counter Latch Command                    |  |

| 0                                    | 0                                            | Select counter 0  |          |                                   |                                          |  |

|                                      | <u>                                     </u> |                   | 0        | 1                                 | Read/Write least significant byte only   |  |

| 0                                    | 1                                            | Select counter 1  |          |                                   |                                          |  |

|                                      |                                              | <u> </u>          | 1        | $\parallel_{0}$                   | Read/Write most significant byte only    |  |

| 1                                    | $\begin{bmatrix} 0 & \end{bmatrix}$          | Select Counter 2  |          |                                   |                                          |  |

| H .                                  | $\parallel \cdot \parallel$                  |                   | 1        | 1                                 | Read/Write least significant byte first, |  |

| $\begin{bmatrix} 1 \\ \end{bmatrix}$ | $\begin{bmatrix} 1 \\ \end{bmatrix}$         | Read-Back command |          |                                   | Then the most significant byte.          |  |

|                                      |                                              | П                 | H I      | II I                              |                                          |  |

Read Back Command: (reading counts on the fly): In some applications, it is necessary to read the value of the count in progress. An appropriate control word is written into control register to latch a count in the output latch and two I/O read operations are performed by MPU.

#### BCD:

| 0 | Binary Counter 16-bits             |

|---|------------------------------------|

| 1 | Binary Coded Decimal (BCD) Counter |

| M2 | M1 | Mo |        |

|----|----|----|--------|

| 0  | 0  | 0  | Mode 0 |

| 0  | 0  | 1  | Mode 1 |

| X  | 1  | 0  | Mode 2 |

| X  | 1  | 1  | Mode 3 |

| 1  | 0  | 0  | Mode 4 |

| 1  | 0  | 1  | Mode 5 |

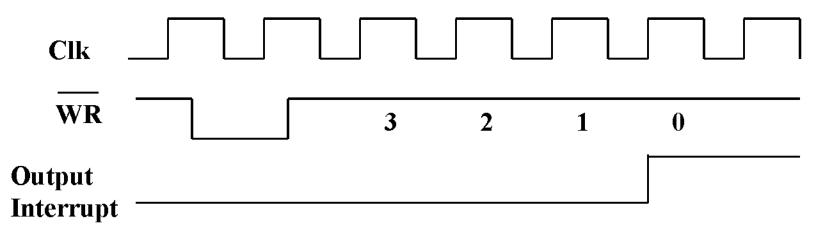

#### **MODE 0: Interrupt on terminal count**

- Initially OUT is low.

- Once Count is loaded in the register, the counter is decremented every cycle.

- When count reaches zero, OUT goes high.

- This can be used as interrupt.

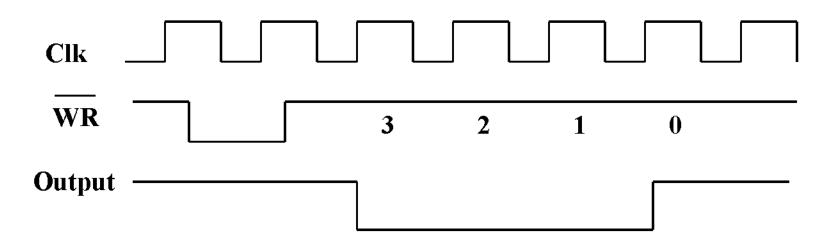

# MODE 1 : HARDWARE-RETRIGGERABLE ONE-SHOT

- •OUT remains initially high.

- When gate is triggered, OUT goes low.

- •At the end of the count the OUT goes high again, thus generating a one shot pulse.

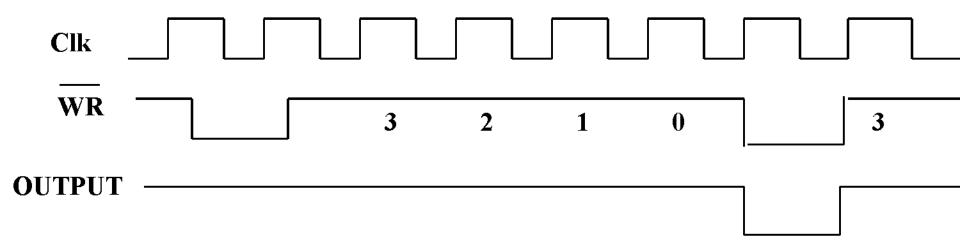

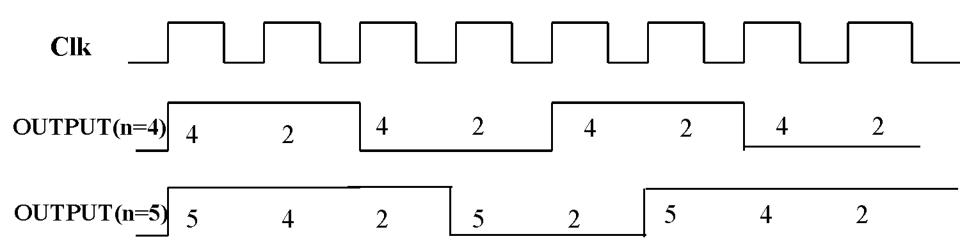

#### **MODE 2 : RATE GENERATOR CLOCK**

- •This mode is used to generate a pulse equal to the clock period at a given interval.

- •When count is loaded, the OUT stays high until count reaches 1.

- •Then the OUT goes low for one clock period.

- •The count is reloaded automatically, and the pulse is generated continuously.

#### **MODE 3 : Square Wave Generator**

- •OUT is high when a count is loaded.

- Count is decremented by 2 at every clock cycle.

- •When it reached 0,OUT goes low and the count is reloaded again.

- •This is repeated continuously this generating a continuous square wave with period equal to period of the count is generated.

#### **MODE 4 : SOFTWARE TRIGGERED STROBE**

In this mode OUT is initially high; it goes low for one clock period at the end of the count. The count must be RELOADED -(UNLIKE MODE 2) for subsequent outputs.

#### **MODE 5: HARWARE TRIGGERED STROBE**

• This mode is similar to MODE 4 except that it is triggered by the rising pulse at the gate. Initially, the OUT is low and when the GATE pulse is triggered from low to high, the count begins. At the end of the count the OUT goes low for one clock period.

#### **READ BACK COMMAND FORMAT:**

• THIS FEATURE AVAILABLE ONLY IN 8254 and not in 8253.

| 1 | 1 | COU | STAT | CNT2 | CNT1 | CNT0 | 0 |

|---|---|-----|------|------|------|------|---|

|   |   |     | US   |      |      |      |   |

|   |   |     |      |      |      |      |   |